# Algorithms and Methods for Fast Model Predictive Control

Gianluca Frison

Kongens Lyngby 2015

Technical University of Denmark

Department of Applied Mathematics and Computer Science

Richard Petersens Plads, building 324,

2800 Kongens Lyngby, Denmark

Phone +45 4525 3031

compute@compute.dtu.dk

www.compute.dtu.dk

PhD-2015-402 ISSN-0909-3192

# Summary (English)

The goal of this thesis is to investigate algorithms and methods to reduce the solution time of solvers for Model Predictive Control (MPC). The thesis is accompanied with an open-source toolbox for High-Performance implementation of solvers for MPC (HPMPC), that contains the source code of all routines employed in the numerical tests. The main focus of this thesis is on linear MPC problems.

In this thesis, both the algorithms and their implementation are equally important. About the implementation, a novel implementation strategy for the dense linear algebra routines in embedded optimization is proposed, aiming at improving the small-scale performance. About the algorithms, they are built on top of the proposed linear algebra, and they are tailored to exploit the high-level structure of the MPC problems, with special care on reducing the computational complexity.

## Preface

This thesis was prepared at the Department of Applied Mathematics and Computer Science (DTU Compute, formerly known as DTU Informatics) at the Technical University of Denmark, in partial fulfillment of the requirements for acquiring a PhD degree in Engineering. The PhD project was founded entirely by DTU Compute; three months as Research Assistant at DTU Compute were founded by EUDP 64013-0558 "Energy Efficient Process Control", and The Danish Council for Strategic Research in the project "CITIES - Centre for IT-Intelligent Energy Systems in Cities" (1305-00027B). All are gratefully acknowledged.

The thesis deals with algorithms and methods for the implementation of fast solvers for model predictive control. The focus of the thesis is on both the optimization algorithms (tailored to exploit the special structure of the model predictive control problem) and the implementation (thanks to a novel implementation strategy for the dense linear algebra routines in embedded optimization). All solvers and routines are gathered in the open-source toolbox HPMPC.

The thesis is in the form of a monograph. The main reason for opting for a monograph instead of a collection of papers is the desire to present the matter in many more details and in a more systematic way than possible in a paper. In particular, the first part of the thesis proposes a novel implementation strategy for the linear algebra routines in embedded optimization, and deep insight and extensive numerical tests are necessary to convince the reader of the effectiveness of the approach.

Kgs. Lyngby, 30-December-2015

Gianluca Frison

# Acknowledgements

First and foremost, I would like to thank my supervisors. John Bagterp Jørgensen for allowing me to pursue what interested me the most, and for his precious advice. Niels Kjølstad Poulsen for his presence and support throughout the project.

I would also like to thank Moritz Diehl for opening me the doors of IMTEK, both during a research stay there, and now for a new adventure.

I would like to thank Milan Vukov and D. Kwame Minde Kufoalor (aka Giorgio) for the endless hours of enthusiastic work together. This project owes you a lot.

Finally, I would like to thank my girlfriend Marie, my family and my friends for their constant support.

# List of abbreviations

ADMM Alternating Direction Method of Multipliers

AS Active-Set

CPU Central Processing Unit

flop floating-point operation

FMA Fused Multiply-Add

FP Floating-Point

Gflops Billions of floating-point operations per second

IPM Interior-Point Method

ISA Instruction Set Architecture

$\mathbf{LLC}$  Last Level of Cache

${f LP}$  Linear Programming

$\mathbf{memop} \ \ \mathbf{memory} \ \mathbf{operation}$

MHE Moving Horizon Estimation

MMU Memory Management Unit

MPC Model Predictive Control

NMHE Nonlinear Moving Horizon Estimation

NMPC Nonlinear Model Predictive Control

$\mathbf{OCP}$  Optimal Control Problem

**QP** Quadratic Programming

${\bf SIMD} \ \ {\bf Single\text{-}Instruction} \ \ {\bf Multiple\text{-}Data}$

$\mathbf{SQP}$  Sequential Quadratic Programming

**TLB** Translation Lookaside Buffer

x Contents

# Contents

| 51     | umm                      | ary (English)                                                                                      | j              |

|--------|--------------------------|----------------------------------------------------------------------------------------------------|----------------|

| P      | refac                    | e                                                                                                  | iii            |

| A      | ckno                     | wledgements                                                                                        | v              |

| Li     | ist of                   | abbreviations                                                                                      | vii            |

| 1<br>[ | 1.1<br>1.2<br>1.3<br>1.4 | ense Linear Algebra Routines for Embedded Opti-                                                    | 4<br>7         |

| 2      | <b>Rev</b> 2.1           | view of dense linear algebra implementation techniques Assumptions about the computer architecture | 17<br>17       |

|        | 2.2                      | Linear algebra routines in high-performance computing: optimized libraries                         | 19<br>19       |

|        |                          | 2.2.1       Reference BLAS and LAPACK                                                              | 21<br>21<br>22 |

xii CONTENTS

|   | 2.4<br>2.5     | 2.3.2 FORCES                                                       | 24<br>25<br>28 |

|---|----------------|--------------------------------------------------------------------|----------------|

| 3 | Lev            | el 3 BLAS and LAPACK for embedded optimization                     | 31             |

|   | 3.1            | General framework: embedded optimization                           | 32             |

|   | 3.2            | Optimizing the gemm routine                                        | 34             |

|   |                | 3.2.1 Optimizing the gemm kernel                                   | 35             |

|   |                | 3.2.2 Use of contiguous memory and panel-major matrix format       | 41             |

|   |                | 3.2.3 Order of outer loops                                         | 43             |

|   |                | 3.2.4 Transposition, edges and corners handling                    | 44             |

|   |                | 3.2.5 Low rank updates handling                                    | 46             |

|   | 3.3            | Optimizing other level 3 BLAS and LAPACK routines                  | 47             |

|   |                | 3.3.1 Triangles, factorizations, substitutions and inversions han- |                |

|   |                | $\operatorname{dling}$                                             | 47             |

|   |                | 3.3.2 Merging of linear algebra routines                           | 49             |

|   |                | 3.3.3 Notable routines                                             | 51             |

|   | 3.4            | Comparison of implementation techniques for dsyrk + dpotrf .       | 54             |

|   | 3.5            | Performance of level 3 BLAS and LAPACK routines                    | 61             |

|   |                | 3.5.1 Performance on Intel Ivy-Bridge micro-architecture           | 62             |

|   |                | 3.5.2 Performance on Intel Haswell micro-architecture              | 64             |

|   |                | 3.5.3 Performance in case of low rank updates                      | 66             |

|   | 3.6            | Conclusion                                                         | 66             |

| 4 | $\mathbf{Lev}$ | el 2 BLAS for embedded optimization                                | 69             |

|   | 4.1            | Optimizing the gemv routine                                        | 71             |

|   |                | 4.1.1 Optimizing the gemv kernel                                   | 72             |

|   |                | 4.1.2 Use of contiguous memory and panel-major matrix format       | 77             |

|   |                | 4.1.3 Edges handling                                               | 78             |

|   | 4.2            | Optimizing the symv routine                                        | 78             |

|   |                | 4.2.1 Optimizing the symv kernel                                   | 79             |

|   | 4.3            | Optimizing other level 2 BLAS routines                             | 84             |

|   |                | 4.3.1 Triangles and substitutions handling                         | 85             |

|   |                | 4.3.2 Merging of linear algebra routines                           | 85             |

|   |                | 4.3.3 Notable routines                                             | 86             |

|   | 4.4            | Performance of level 2 BLAS routines                               | 87             |

|   |                | 4.4.1 Performance on Intel Ivy-Bridge micro-architecture           | 87             |

|   | 4 5            | 4.4.2 Performance on Intel Haswell micro-architecture              | 88             |

|   | 4.5            | Conclusion                                                         | 90             |

| 5 | Opt            | imizing gemm kernels on different architectures                    | 93             |

|   | 5.1            | x86                                                                | 94             |

|   |                | 5.1.1 Intel Bonnell (Atom)                                         | 95             |

|   | 5.2            | x86 64                                                             | 99             |

CONTENTS xiii

|         |                                          | 5.2.1 Intel Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                |

|---------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|         |                                          | 5.2.2 Intel Nehalem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                               |

|         |                                          | 5.2.3 Intel Sandy-Bridge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6                                                                                                                                |

|         |                                          | 5.2.4 Intel Haswell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3                                                                                                                                |

|         |                                          | 5.2.5 Intel Skylake                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7                                                                                                                                |

|         |                                          | 5.2.6 AMD K10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8                                                                                                                                |

|         | 5.3                                      | ARMv7A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                |

|         |                                          | 5.3.1 ARM Cortex A9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                |

|         |                                          | 5.3.2 ARM Cortex A15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7                                                                                                                                |

|         |                                          | 5.3.3 ARM Cortex A7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

|         | 5.4                                      | ARMv8A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                  |

|         |                                          | 5.4.1 Cortex A57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

|         | 5.5                                      | PowerPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                  |

|         |                                          | 5.5.1 PowerPC 603e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                  |

|         | 5.6                                      | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                |

| 6       | Sun                                      | nmary and considerations about code generation 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q                                                                                                                                |

| U       | 6.1                                      | Comparison with existing dense linear algebra implementations . 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                  |

|         | U -                                      | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                |

|         |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                  |

| II      |                                          | lgorithms for Unconstrained MPC and MHE Prob-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | a                                                                                                                                |

|         | $\mathbf{m}_{\mathbf{s}}$                | lgorithms for Unconstrained MPC and MHE Prob- $14$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9                                                                                                                                |

|         | ms                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

| le      | ms                                       | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                |

| le      | ms<br>Uno                                | onstrained MPC and MHE problem formulations 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>1</b>                                                                                                                         |

| le      | ms<br>Uno                                | onstrained MPC and MHE problem formulations Unconstrained MPC problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1<br>51<br>52                                                                                                                    |

| le      | ms<br>Uno                                | Onstrained MPC and MHE problem formulations         15           Unconstrained MPC problem         15           7.1.1 Marix formulation         15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1<br>1<br>52<br>53                                                                                                               |

| le      | ms<br>Uno<br>7.1                         | 14           onstrained MPC and MHE problem formulations         15           Unconstrained MPC problem         15           7.1.1 Marix formulation         15           7.1.2 Optimality conditions         15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $egin{array}{c} 1 \\ 52 \\ 53 \\ 54 \end{array}$                                                                                 |

| le      | ms<br>Uno<br>7.1                         | 14           onstrained MPC and MHE problem formulations         15           Unconstrained MPC problem         15           7.1.1 Marix formulation         15           7.1.2 Optimality conditions         15           Unconstrained MHE problem         15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1<br>1<br>3<br>4<br>5                                                                                                            |

| le<br>7 | ms Unc 7.1                               | 14           onstrained MPC and MHE problem formulations           Unconstrained MPC problem         15           7.1.1 Marix formulation         15           7.1.2 Optimality conditions         15           Unconstrained MHE problem         15           7.2.1 Matrix formulation         15           7.2.2 Optimality conditions         15                                                                                                                                                                                                                                                                                                                                                                                                                                | 1<br>1<br>3<br>4<br>5                                                                                                            |

| le      | ms Unc 7.1 7.2                           | 14           constrained MPC and MHE problem formulations         15           Unconstrained MPC problem         15           7.1.1 Marix formulation         15           7.1.2 Optimality conditions         15           Unconstrained MHE problem         15           7.2.1 Matrix formulation         15           7.2.2 Optimality conditions         15           acture-exploiting recursive factorizations of the KKT ma-                                                                                                                                                                                                                                                                                                                                                | 1<br>1<br>3<br>3<br>4<br>5<br>6                                                                                                  |

| le<br>7 | Unc<br>7.1<br>7.2<br>Stru<br>trix        | 14         constrained MPC and MHE problem formulations         Unconstrained MPC problem       15         7.1.1 Marix formulation       15         7.1.2 Optimality conditions       15         Unconstrained MHE problem       15         7.2.1 Matrix formulation       15         7.2.2 Optimality conditions       15         acture-exploiting recursive factorizations of the KKT ma-       15                                                                                                                                                                                                                                                                                                                                                                              | 1<br>51<br>53<br>54<br>55<br>6                                                                                                   |

| le<br>7 | ms Unc 7.1 7.2                           | 14           onstrained MPC and MHE problem formulations           Unconstrained MPC problem         15           7.1.1 Marix formulation         15           7.1.2 Optimality conditions         15           Unconstrained MHE problem         15           7.2.1 Matrix formulation         15           7.2.2 Optimality conditions         15           acture-exploiting recursive factorizations of the KKT ma-           Backward riccati recursion         15                                                                                                                                                                                                                                                                                                            | 1<br>51<br>53<br>54<br>55<br>66                                                                                                  |

| le<br>7 | Unc<br>7.1<br>7.2<br>Stru<br>trix        | 14           onstrained MPC and MHE problem formulations           Unconstrained MPC problem         15           7.1.1 Marix formulation         15           7.1.2 Optimality conditions         15           Unconstrained MHE problem         15           7.2.1 Matrix formulation         15           7.2.2 Optimality conditions         15           acture-exploiting recursive factorizations of the KKT ma-         15           Backward riccati recursion         15           8.1.1 Derivation         15                                                                                                                                                                                                                                                           | 1<br>1<br>3<br>4<br>5<br>6<br>7<br>8<br>9                                                                                        |

| le<br>7 | unc<br>7.1<br>7.2<br>Stru<br>trix<br>8.1 | 14         constrained MPC and MHE problem formulations         Unconstrained MPC problem       15         7.1.1 Marix formulation       15         7.1.2 Optimality conditions       15         Unconstrained MHE problem       15         7.2.1 Matrix formulation       15         7.2.2 Optimality conditions       15         acture-exploiting recursive factorizations of the KKT ma-       15         Backward riccati recursion       15         8.1.1 Derivation       15         8.1.2 Implementation       16                                                                                                                                                                                                                                                          | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1                                      |

| le<br>7 | unc<br>7.1<br>7.2<br>Stru<br>trix<br>8.1 | 14           constrained MPC and MHE problem formulations         15           Unconstrained MPC problem         15           7.1.1 Marix formulation         15           7.1.2 Optimality conditions         15           Unconstrained MHE problem         15           7.2.1 Matrix formulation         15           7.2.2 Optimality conditions         15           acture-exploiting recursive factorizations of the KKT ma-         15           Backward riccati recursion         15           8.1.1 Derivation         15           8.1.2 Implementation         16           Forward Schur-complement recursion         17                                                                                                                                             | 1<br>51<br>53<br>54<br>55<br>66<br>7<br>89<br>84<br>70                                                                           |

| le<br>7 | unc<br>7.1<br>7.2<br>Stru<br>trix<br>8.1 | 14         constrained MPC and MHE problem formulations         Unconstrained MPC problem       15         7.1.1 Marix formulation       15         7.1.2 Optimality conditions       15         Unconstrained MHE problem       15         7.2.1 Matrix formulation       15         7.2.2 Optimality conditions       15         Icture-exploiting recursive factorizations of the KKT ma-         Backward riccati recursion       15         8.1.1 Derivation       15         8.1.2 Implementation       16         Forward Schur-complement recursion       17         8.2.1 Derivation       17                                                                                                                                                                             | 1<br>51<br>52<br>53<br>54<br>55<br>65<br>7<br>7<br>8<br>9<br>7<br>1                                                              |

| le<br>7 | unc<br>7.1<br>7.2<br>Stru<br>trix<br>8.1 | 14           onstrained MPC and MHE problem formulations           Unconstrained MPC problem         15           7.1.1 Marix formulation         15           7.1.2 Optimality conditions         15           Unconstrained MHE problem         15           7.2.1 Matrix formulation         15           7.2.2 Optimality conditions         15           acture-exploiting recursive factorizations of the KKT ma-         15           Backward riccati recursion         15           8.1.1 Derivation         15           8.1.2 Implementation         16           Forward Schur-complement recursion         17           8.2.1 Derivation         17                                                                                                                   | 1<br>51<br>52<br>53<br>54<br>55<br>66<br>70<br>77<br>77                                                                          |

| le<br>7 | *ms Unc 7.1 7.2 Strutrix 8.1 8.2         | 14           constrained MPC and MHE problem formulations           Unconstrained MPC problem         15           7.1.1 Marix formulation         15           7.1.2 Optimality conditions         15           Unconstrained MHE problem         15           7.2.1 Matrix formulation         15           7.2.2 Optimality conditions         15           acture-exploiting recursive factorizations of the KKT ma-         15           8.1.1 Derivation         15           8.1.2 Implementation         16           Forward Schur-complement recursion         17           8.2.1 Derivation         17           8.2.2 Implementation         17           8.2.2 Implementation         17           8.2.2 Implementation         17                                    | 1<br>51<br>52<br>53<br>54<br>54<br>56<br>66<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7 |

| le<br>7 | *ms Unc 7.1 7.2 Strutrix 8.1 8.2         | 14           constrained MPC and MHE problem formulations           Unconstrained MPC problem         15           7.1.1 Marix formulation         15           7.1.2 Optimality conditions         15           Unconstrained MHE problem         15           7.2.1 Matrix formulation         15           7.2.2 Optimality conditions         15           acture-exploiting recursive factorizations of the KKT ma-         15           Backward riccati recursion         15           8.1.1 Derivation         15           8.1.2 Implementation         16           Forward Schur-complement recursion         17           8.2.1 Derivation         17           8.2.2 Implementation         17           Comparison of structure-exploiting factorizations         18 | 1<br>51<br>53<br>54<br>54<br>69<br>77<br>77<br>77<br>72<br>23                                                                    |

xiv CONTENTS

| 9  | Con  |                                                             | 197         |

|----|------|-------------------------------------------------------------|-------------|

|    | 9.1  | Condensing methods for MPC                                  | 198         |

|    |      | 9.1.1 Condensing algorithms for MPC                         | 200         |

|    |      | 9.1.2 Factorization algorithms for MPC                      | 214         |

|    |      | 9.1.3 Condensing and factorization algorithms for MPC       | 218         |

|    |      | 9.1.4 Solution algorithms for MPC                           | 224         |

|    | 9.2  | Condensing methods for MHE                                  |             |

|    |      | 9.2.1 Condensing algorithms for MHE                         |             |

|    |      | 9.2.2 Factorization algorithms for MHE                      |             |

|    |      |                                                             |             |

|    |      | 9.2.4 Solution algorithms for MHE                           |             |

|    | 9.3  | Conclusion                                                  |             |

| 10 | Part | tial condensing                                             | 255         |

|    |      | Partial condensing algorithms                               | 259         |

|    |      | Choice of $N_p$                                             |             |

|    |      | Influence of linear algebra routines performance            |             |

|    |      | Conclusion                                                  |             |

| 11 | Unc  | constrained MPC problems with time-invariant matrices       | 267         |

|    |      | Problem formulation                                         | 268         |

|    |      | Motivation                                                  |             |

|    |      |                                                             |             |

|    |      |                                                             | 269         |

|    |      | 11.2.3 Sub-problem in splitting methods for constrained LQR | 270         |

|    | 11.3 | Sparse formulation                                          |             |

|    |      | Condensed formulation                                       |             |

|    |      | Implementation aspects                                      |             |

|    |      | Conclusion                                                  |             |

|    |      |                                                             |             |

| II | I A  | Algorithms for Constrained and Non-Linear MPC2              | 277         |

| 12 |      |                                                             | 279         |

|    | 12.1 | Linear MPC problem                                          | 280         |

|    |      | 12.1.1 Matrix formulation                                   | 281         |

|    |      | 12.1.2 Optimality conditions                                | 282         |

| 13 | Solu | ntion of sub-problems in linear MPC and MHE problems        | <b>28</b> 5 |

|    | 13.1 | Interior-point methods                                      | 286         |

|    |      | 13.1.1 Basics about interior-point methods                  | 286         |

|    |      | 13.1.2 Interior-point methods for the linear MPC problem    | 288         |

|    |      | 13.1.3 Interior-point methods implementation choices        | 289         |

|    |      | 13.1.4 Partial condensing for linear MPC problems           | 290         |

CONTENTS xv

|     |       | Alterna<br>13.2.1<br>13.2.2<br>13.2.3<br>13.2.4<br>13.2.5 | Comparison of solvers for linear MPC problems ating direction method of multipliers  Notation and basics about ADMM  Box constraints  Soft constraints  ADMM implementation choices  Numerical results for the linear MPC problem asion | <br> | <br> | 298<br>298<br>299<br>300<br>302<br>303 |

|-----|-------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------------------------------------|

|     | nonl  | linear I                                                  | and considerations about solution of sub-pr<br>MPC and MHE problems<br>ce with existing solvers for NMPC                                                                                                                                |      |      | 307                                    |

| A   | Cus   | tom go                                                    | c Compiler                                                                                                                                                                                                                              |      |      | 311                                    |

| Bil | oliog | raphy                                                     |                                                                                                                                                                                                                                         |      |      | 317                                    |

xvi CONTENTS

### CHAPTER 1

## Introduction

The aim of this thesis is to investigate algorithms and methods to reduce the solution time of solvers for Model Predictive Control (MPC). The thesis is accompanied with an open-source toolbox for High-Performance implementation of solvers for MPC (HPMPC), that contains the source code of all routines employed in the numerical tests [29]. The main focus of this thesis is on linear MPC problems, in that they arise as sub-problems in some Nonlinear MPC (NMPC) formulations.

#### 1.1 Background

MPC is an advanced control technique that gained much attention in both academia and industry in the last few decades, for both the linear and nonlinear MPC cases [68]. Good introductions to MPC can be found in [60, 71, 70]. In a few sentences, MPC makes use of a model of the controlled plant to predict its future state and compute an input (also known as controls or manipulated variables) sequence optimal with respect to both performance metrics and plant constraints. MPC can deal with complex plants with several inputs and outputs (also known as controlled variables) and relative constraints, and incorporate in a predictive way information about set-point changes or known disturbances. This is achieved by solving at each sampling instant an optimization problem,

that is parametrized with respect to the current state of the plant. The need to efficiently and reliably solve this optimization problem at each sampling instant, as soon as a new estimate of the plant state is available, has traditionally limited the application of MPC to the control of plant with slow dynamic. There has been much research effort in improving the solution time of the optimization problems in MPC, that is a necessary condition for the applicability of MPC to the control of systems characterized by faster dynamic.

In the last few decades, MPC has been successfully applied to the control of systems characterized by increasingly faster dynamic, from the sampling times in the order of minutes all the way down to sampling times up to MHz rates [48]. Much of these improvements have been achieved thanks to the development of optimization algorithm tailored to the special structure of the MPC problem. The two main research directions in this field are off-line and on-line solution methods of the MPC problem.

Explicit MPC [20, 19] exploits the fact that the solution of the constrained linear MPC problem is a continuous piecewise affine function of the state over a polyhedral partition, and that it can be precomputed off-line for all initial states. The on-line part of the algorithm reduces to a lookup table, and therefore extremely high control frequencies can be achieved. Since in the worst case the number of regions can be as large as the combinations of active constraints, the use of explicit MPC is generally limited to very small MPC problems.

Alternatively, the solution of the optimization problems can be computed online, between two sampling instants. This imposes tight real-time requirements on the execution time of the solvers, requiring the development of reliable solution methods for optimization problems with the structure of MPC problems. Suitable solvers must be certified to return the solution within the available time, or at least should return a reasonable approximation of the solution if stopped early. On-line methods comprise first and second order optimization methods.

First order optimization methods (such as gradient methods [72, 49, 57] and splitting methods [81, 67]) are generally straightforward to implement and can easily exploit sparsity pattern and special structure of problems. They perform many but cheap iterations, where the cost-per-iteration is quadratic in the input and state size (requiring level 2 BLAS operations as e.g a matrix-vector multiplication or solution of a system of linear equation whose matrix is factorized off-line). In general, the number of iterations (and therefore the solution time) can vary significantly with the number of active constraints and the problem conditioning. Therefore, there has been much effort in finding certification on the solution time of these methods [73].

1.1 Background 3

Second order optimization methods make use of second order information to converge to a solution in fewer iterations. Interior-Point Methods (IPM) and Active-Set methods (AS) belong to this class. In the IPM case, there exists a polynomial certification on the number of iterations required for convergence, but it is very loose and therefore of no practical value. In practice, in IPMs the number of iterations is rather unaffected by the problem instance: if well initialized, these methods can typically converge to the solution in 8-15 iterations. This justifies the wide use of IPMs in MPC [69, 88, 61, 25]. Each iteration is more computationally heavy that in the first order methods case, requiring the factorization and solution of a system of linear equations in the computation of the search direction. The factorization makes use of level 3 BLAS and therefore requires a cubic number of flops in the input and state size.

There is not a polynomial certification for the AS methods, that in the worst case can require an exponential number of iterations to converge. However, in practice AS methods perform well, and can return a solution quickly, and therefore they find wide applicability in MPC [53, 65]. Particularly interesting is the approach employed in the open-source AS solver qpOASES [27, 28], that, in case of early stop, returns the solution of a QP that is between the one solved at the previous sampling instant and the current one. AS methods typically require more iterations than IPM to converge, but the iterations are generally cheaper, since the KKT matrix can be updated without the need to re-factorize it, when there are changes in the active set.

The other factor contributing to the reduction in solution times has been the improvement in the computer hardware. In particular, processor frequencies have increased exponentially for about two decades, going from a few MHz at the beginning of the '80s, to about 3 GHz with the introduction of Intel Pentium 4 in 2002. In general, an increase in the CPU frequency translates directly in a similar increase in performance. Therefore, there has not been the need to invest much research effort on the implementation side. However, since then the CPU frequencies have stalled, and further improvements in computing power can come only from the use of vector execution units or multiple CPU core, both requiring additional programming effort [83].

Probably due to the fact that matrices in MPC problems are generally of small size, the use of optimized BLAS libraries has not been considered of much help in implementing fast solvers for MPC or MHE [45]. An implementation technique that recently gained much traction in the field of MPC is code generation, originally proposed in this field in [61]. The idea of code generation is to exploit the fact that, in MPC, problems of fixed structure are repeatedly solved at each sampling instant. This can be done e.g. by choosing the best solution strategy for the problem at hand, or by exploiting sparsity and knowledge about the size of matrices. In the implementation of linear algebra routines, all loops can

be totally unrolled (as in [61]), or the size of the loops can be fixed at code generation time (as in [25]).

#### 1.2 Thesis approach

As stated in the title, the thesis deals with algorithms and methods for fast model predictive control. Methods mainly refers to Part I of the thesis (dealing with linear algebra implementation methods), while algorithms mainly refers to Part II and Part III of the thesis (dealing with tailored algorithm for MPC). Both algorithm and implementation are considered equally important in the development of fast solvers.

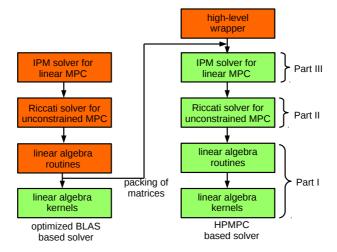

The structure of the thesis follows the structure of the HPMPC toolbox, as shown on the right hand side of Figure 1.1. Part I deals with the efficient implementation of linear algebra routines for embedded optimization, and that forms the basis for the developed solvers. Part II deals with solvers for unconstrained MPC and MHE problems. Part III deals with solvers for linear (constrained) MPC and MHE problems.

The approach used in the solvers development is to implement a toolbox of efficient dense linear algebra routines, and to explicitly exploit the structure and sparsity pattern of the MPC problems in the algorithms implemented using these routines.

Part I of the thesis proposes a novel implementation strategy for dense linear algebra routines, specially tailored for embedded optimization. The matrices of interest in embedded optimization are typically of small to medium size, and they can generally fit in cache. Therefore, some of the implementation techniques employed in optimized BLAS libraries (such as blocking for cache) give no advantages, on the contrary they decrease the performance due to the overhead of performing useless operations (that is particularly true in case of small matrices). Therefore, a subset of BLAS and LAPACK has been re-implemented using only techniques beneficial to the embedded optimization case, such as blocking for registers and explicit use of vectorization through SIMD instructions. Only single-thread code has been considered in this thesis, as parallel computation is mostly beneficial for larger size problems, and in any case it should be employed only once the single thread performance has been well optimized.

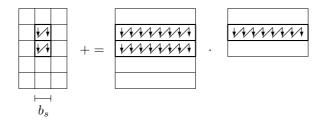

Furthermore, a special matrix format is proposed, called panel-major matrix format. It consists of horizontal panels (i.e. sub-matrices with few rows and many columns) of fixed height  $b_s$  stored one after the other, with the elements

Figure 1.1: Structure of a Riccati-based IPM for linear MPC problems when implemented using linear algebra in either optimized BLAS or HPMPC. Routines in the orange boxes use matrices in column-major format, routines in the green boxes use matrices in panel-major format (or equivalent internal format in optimized BLAS). The thesis follows the structure of the HPMPC toolbox, with Part I dealing with linear algebra, Part II with solvers for unconstrained MPC problems and Part III with solvers for linear (constrained) MPC problems.

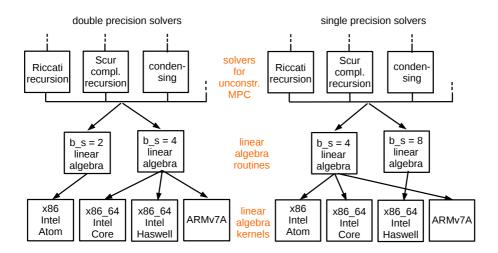

Figure 1.2: Structure of the linear algebra routines in HPMPC. The linear algebra kernels are tailored to each computer architecture. The linear algebra routines depend only on the panel height  $b_s$  (that may be different for single and double precision). The routines at higher levels in the routines hierarchy are completely architecture-independent.

within each panel stored in column-major order. This matrix format roughly corresponds to the innermost level of packing employed in optimized BLAS libraries, giving optimal performance for matrices fitting in cache (as typical in embedded optimization). The fundamental difference is that in optimized BLAS libraries the packing of matrices into this format is done at each call to a linear algebra routine, while in the proposed approach the panel-major matrix format is the format expected by linear algebra routines, as shown in Figure 1.1. This moves the overhead of packing matrices from the standard column-major or row-major formats much higher in the routines hierarchy. In particular, in embedded optimization the packing overhead can be well amortized over the iterations of the optimization methods.

The innermost loop of each linear algebra routine is coded in a separate function, the kernel. The linear algebra kernels are typically coded in assembly or using intrinsics, and are tailored for a number of computer architectures, as shown in Figure 1.2. The two outermost loops of linear algebra routines are almost architecture-independent, in the sense that they are coded in C code but they depend on the panel height  $b_s$ . All routines at higher levels in the routines hierarchy are completely architecture-independent.

1.3 Thesis outline 7

Part II of the thesis deals with algorithms for unconstrained MPC and MHE problems. The focus of these algorithms is on exploiting the structure and the sparsity pattern of the unconstrained MPC and MHE problems at the algorithm level, since the underlying linear algebra routines are dense.

About the choice of the algorithms, two structure-exploiting factorizations of the KKT matrix of the unconstrained MPC and MHE problems are presented. Namely, the backward Riccati recursion and the forward Schur-complement method are reviewed, and their efficient implementation in HPMPC is presented in details. None of these methods is novel in the field of MPC, but the level of performance obtained by the routines in HPMPC has not been obtained before, to the best of my knowledge. Furthermore, a collection of algorithms for condensing of MPC and MHE problems is presented. Some of the algorithms are well known, some are novel (to the best of my knowledge). Structure-exploiting factorizations and condensing methods find a conjunction point in partial condensing, that is a technique recently proposed to trade-off the horizon length and the input size in MPC and MHE problems [17].

Part III of the thesis briefly deals with algorithms for linear (constrained) MPC and MHE problems. In particular, two algorithms are presented: an IPM and an ADMM (Alternating Direction Method of Multipliers), both employing the backward Riccati recursion as a routine to solve tailored systems of linear equations. The focus is on showing as the special structure of the constraints can be exploited to efficiently handle them.

#### 1.3 Thesis outline

Chapter 1 contains the introduction, comprising background, thesis approach, thesis structure and publication list. Afterwards, the thesis is divided into three parts.

**Part I** deals with efficient implementation methods for dense linear algebra routines, tailored for embedded optimization applications.

Chapter 2 states assumptions about the structure of the computer architectures considered in this thesis. Afterwards, it contains a brief review of the main approaches employed in the implementation of optimized BLAS libraries and in the implementation of linear algebra routines in embedded optimization. Finally, it compares the computational performance of the more promising options

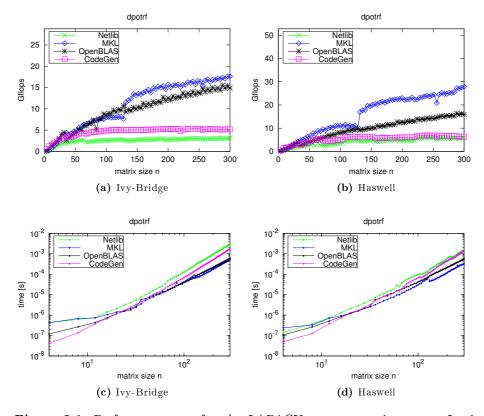

currently available for the implementation of the dense Cholesky factorization for small to medium matrices.

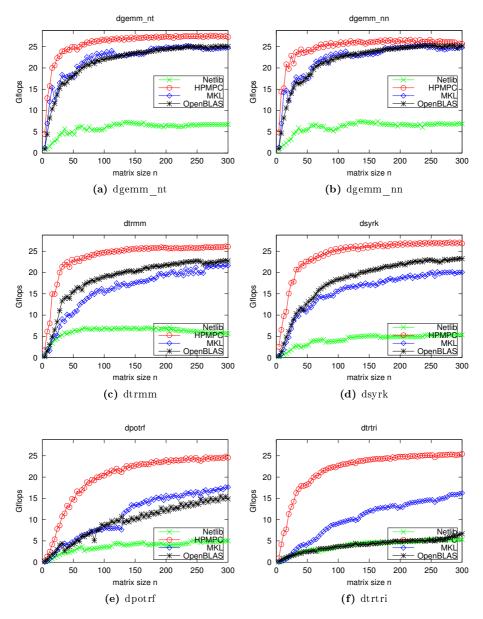

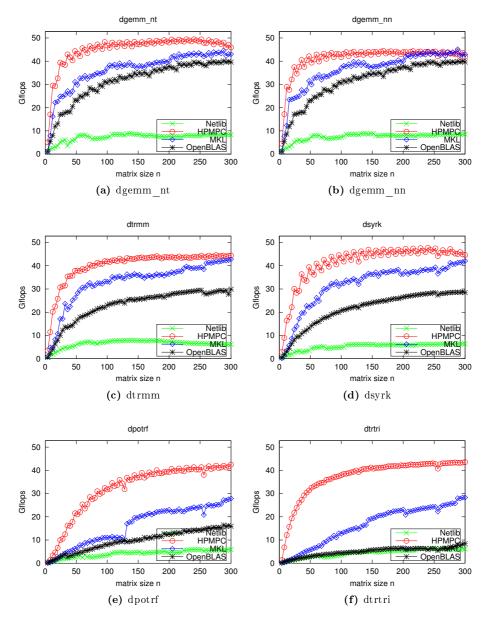

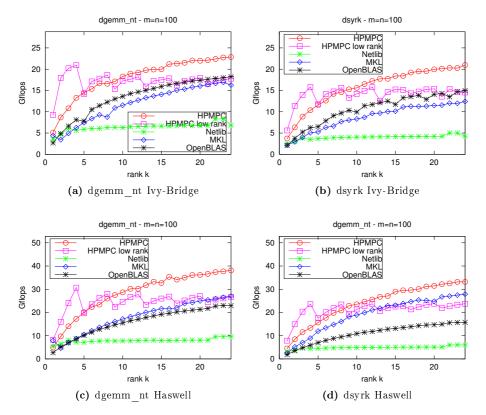

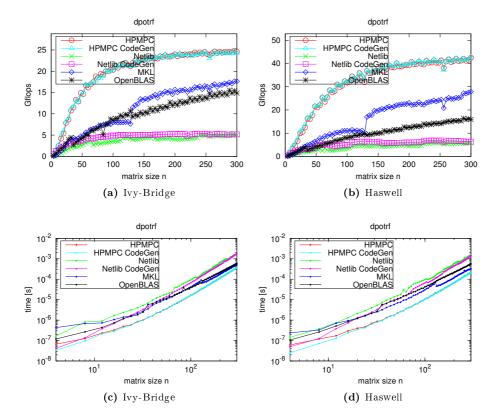

Chapter 3 proposes a novel implementation method for level 3 BLAS and LAPACK routines (that are the backbone of algorithms for KKT matrix factorization and Hessian condensing), specially tailored for embedded optimization applications. The chapter begins with some assumption about the nature of the embedded optimization problems, and the consequences for the implementation of linear algebra routines. Afterwards, it presents a set of optimization techniques that provides good performance for small matrices, and it proposes a novel matrix format, that guarantees optimal performance of level 3 BLAS routines for matrices roughly fitting in last level cache. The step-by-step optimization of a key routine shows the performance impact of each single implementation technique. Finally, a selection of common level 3 BLAS and LAPACK routines is compared on two recent computer architectures, and the proposed approach is compared with the best proprietary and open-source BLAS libraries.

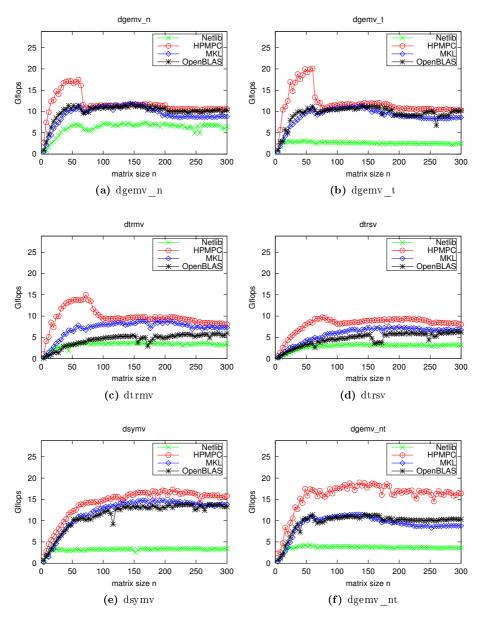

Chapter 4 is analogue to Chapter 3 but focusing on level 2 BLAS routines (that are the backbone of algorithms for KKT matrix solution, Jacobian condensing and residuals computation).

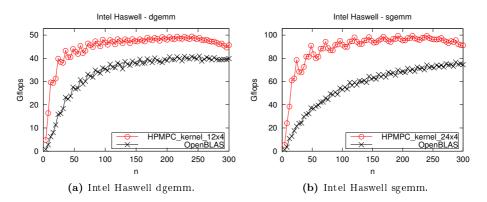

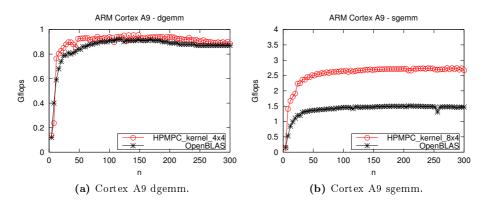

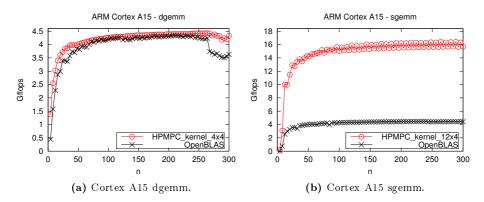

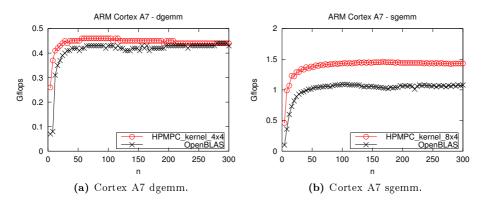

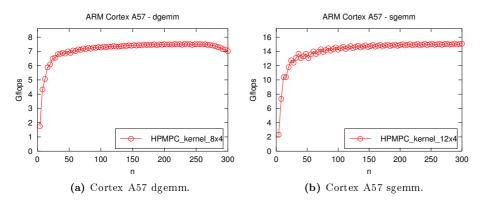

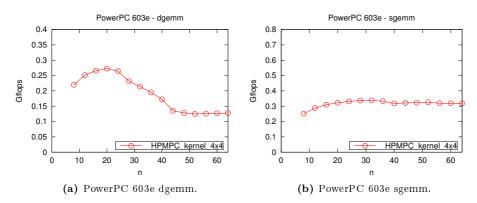

Chapter 5 introduces a number of common computer architectures, and describes in details the optimization of the general matrix-matrix multiplication gemm kernel on the different architectures, in both single and double precision.

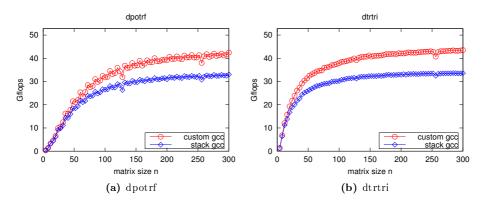

Chapter 6 contains the summary of the Part I, and adds the Cholesky factorization routine implemented using the proposed methods to the initial performance tests performed in Chapter 2. Furthermore, it investigates if the use of code generation can further improve performance.

**Part II** contains a collection of structure-exploiting methods for the solution of unconstrained (linear) MPC and MHE problems. These methods are implemented using the efficient linear algebra routines proposed in Part I.

Chapter 7 introduces the unconstrained MPC and MHE problem formulations considered in the remaining of the part, and shows the structure of the KKT matrices for these problems.

1.3 Thesis outline 9

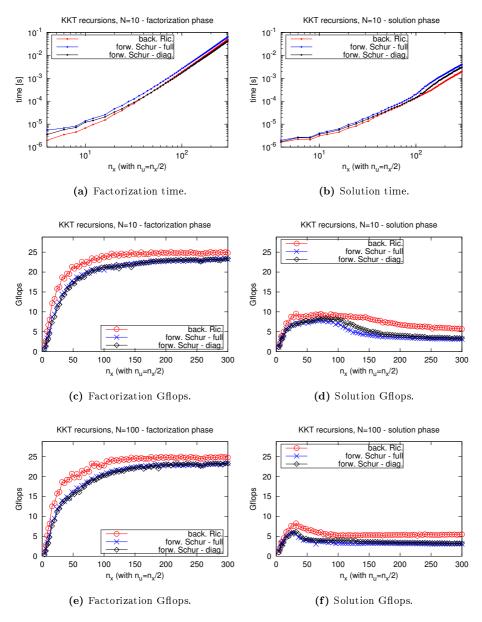

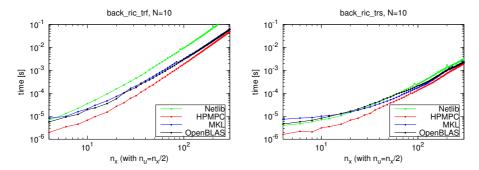

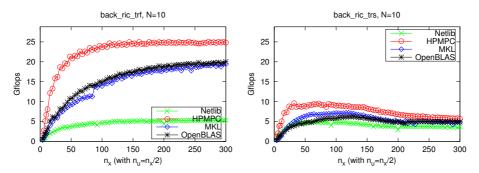

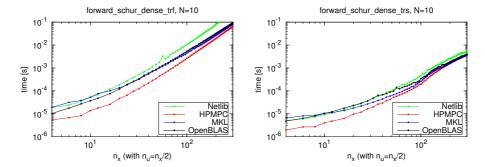

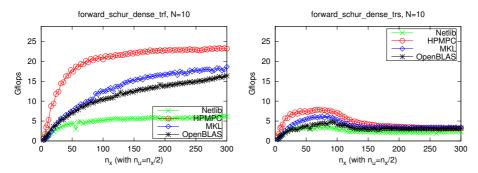

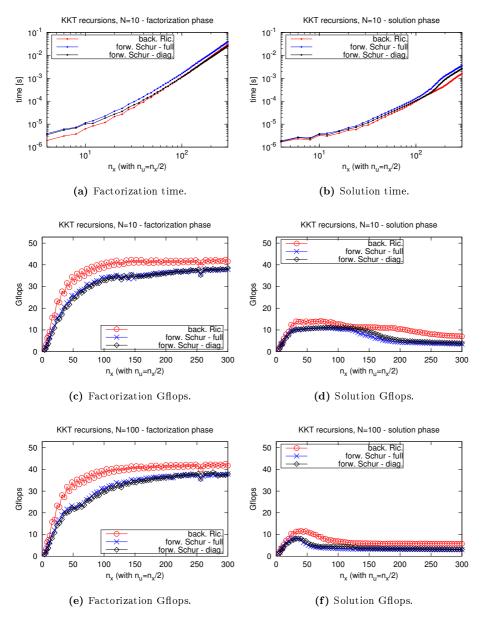

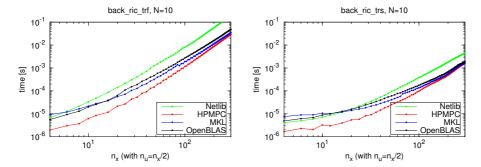

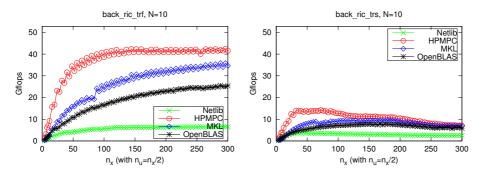

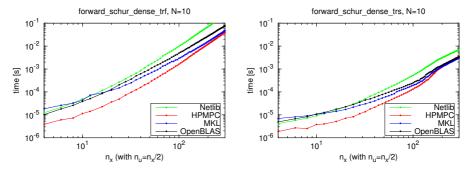

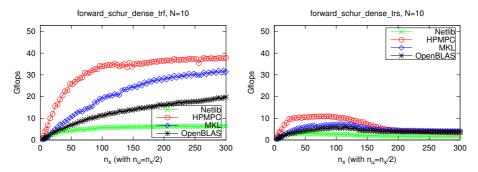

Chapter 8 presents two structure-exploiting factorizations for the KKT matrix of the unconstrained MPC and MHE problems: a backward Riccati recursion and a forward Schur-complement recursion. Implementation of these routines using both optimized BLAS libraries and the custom linear algebra routines proposed in Part I are presented in details. Finally, exhaustive tests compare the performance of the two recursions, when implemented using optimized BLAS libraries or the proposed custom linear algebra routines.

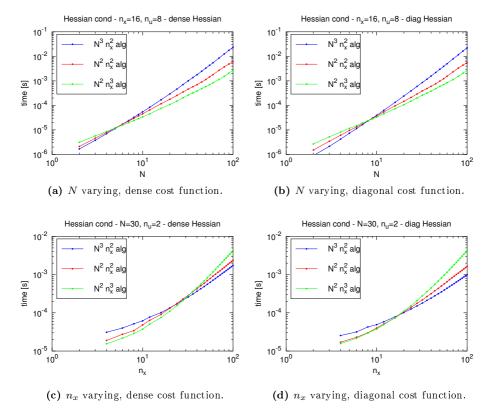

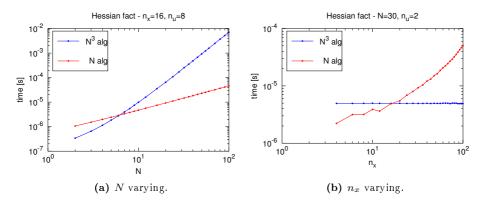

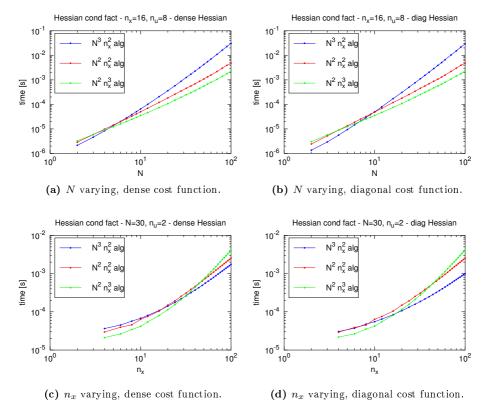

Chapter 9 presents a wide collection of condensing methods for the MPC and MHE problems. All algorithms are initially presented for the MPC problem, and afterwards adapted to the MHE problem by considering the free initial state as an extra input variable at stage -1. In particular, three Hessian condensing methods (with one novel to the best of my knowledge), two Hessian factorization methods (with one novel to the best of my knowledge) and two Hessian solution methods (with one novel to the best of my knowledge) are presented. Furthermore, two combined methods for the simultaneous condensing and factorization of the Hessian matrix are presented by combining two Hessian condensing methods with the novel Hessian factorization method (one of the resulting algorithms is novel the best of my knowledge). The asymptotic complexity of all methods is analyzed both as number of flops and as execution time (with linear algebra routines implemented as described in Part I).

Chapter 10 reviews the idea of partial condensing and proposes efficient algorithms for the computation of the state space equations and cost function matrices and vector in the partially condensed MPC and MHE problems. The algorithms are based on the best algorithm for the Hessian condensing of the MHE problem, as investigated in Chapter 10. Furthermore, the backward Riccati recursion of Chapter 8 is used as an example to derive theoretical guidelines on the best value for the horizon length in the partially condensed MPC and MHE problems. Finally, the influence of the performance of linear algebra routines is investigated, finding that partial condensing gives additional performance advantages in case of very small matrices (to the best of my knowledge, this has not been investigated in literature yet).

Chapter 11 tailors the backward Riccati recursion and the novel Hessian condensing and solution methods to the special case of MPC problems with time-invariant matrices and time-variant vectors, in both the state space equations and the cost function expression, in the special case of the matrix of the terminal cost initialized to the solution of the discrete Riccati algebraic equations. Situations where problems in this form arise are described; in particular, problems in

this form arise as sub-problems in splitting methods for the constrained linear quadratic regulator. Problems in this form can be solved extremely efficiently, since the backward structure-exploiting factorization gives matrices constant over the stages. Therefore, there is no need to perform the factorization over all the stages, and only the matrices of a single stage need to be stored, greatly decreasing the memory requirements for the algorithms (these considerations are, to the best of my knowledge, novel).

**Part III** deals with algorithms for constrained (linear) MPC and MHE problems, that are implemented using the solvers from Part II as routines. Only algorithms for MPC are explicitly considered, the algorithms for MHE being analogue.

Chapter 12 introduces the linear (constrained) MPC formulations considered in the remaining of the part. In particular, hard and soft box constraints and general polytopic constraints are considered.

Chapter 13 presents two Riccati-based optimization methods for the solution of linear MPC problems: an IPM and an ADMM. These optimization methods have been widely used in literature, and have been chosen here in that they can benefit from an efficient implementation of the backward Riccati recursion. Furthermore, techniques to exploit the special structure of the soft constraints are presented, and numerical tests confirm that linear MPC problems with soft constraints can be solved in only slightly more time than the hard-constrained counterparts. The resulting IPM solvers are found to be more than an order of magnitude faster than a successful state-of-the-art solver for embedded optimization on a widely used benchmark, for medium to large problems. Furthermore, the overhead of the high-level wrapper is well amortized over the IPM iterations.

Chapter 14 contains a summary of Part III, and it shows the performance gains obtained using the efficient Riccati-based IPM solver and the forward Schur-complement recursion as routines in the real-time solution of challenging NMPC and NMHE problems using ACADO.

**Appendix A** proposes a modification to the open-source compiler gcc to improve the performance of the intrinsics for the various fused multiply-subtraction

1.4 Publications list 11

instructions (employed e.g. in the implementation of the Cholesky factorization) in the x86 64 FMA ISA.

#### 1.4 Publications list

The following journal articles ('article') and conference proceedings ('paper' or 'abstract') were published during the project period.

Paper [32] deals with algorithms for the solution of the unconstrained MPC problem, that make use of optimized BLAS and LAPACK routines in Open-BLAS [93] for the linear algebra. The first part of the paper reports some results originally found in the MSc thesis [30]: the backward Riccati recursion is found to be the solution method performing better for the widest range of problem sizes, in case of dense matrices in the state space equation and cost function formulation. The second part of the paper proposes techniques to improve the speed of a Riccati-based solver, such as the use of the Cholesky factorization to reduce the flop count (as shown in Chapter 8), or the use of mixed precision computation [22] (that is orthogonal to the techniques presented in this thesis).

Paper [76] presents an efficient IPM for the LPs arising in economic MPC of linear systems. The IPM combines a homogeneous and self-dual model with a specialized Riccati recursion, and it is tested on a power system management test problem. The subject of the paper is no further considered in this thesis.

Paper [34] compares techniques to parallelize the Cholesky factorization routine in the implementation of the backward Riccati recursion. In particular, the performance of the parallel version of OpenBLAS [93] is compared to the performance of PLASMA [13], that is a library providing LAPACK-like routines where multiple threads are explicitly handled in the linear algebra algorithms instead of in the level 3 BLAS routines. Furthermore, the asyncronous version of PLASMA allows for the threads of linear algebra routines to be scheduled asyncronously, while explicit barriers are employed to ensure correctness of the results. The subject of the paper is no further considered in this thesis, since the focus in on single-thread code.

Paper [33] proposes structure-exploiting condensing methods for the solution of the unconstrained MPC problem. In particular, two Hessian condensing

algorithms are considered, together with a novel structure-exploiting Hessian factorization and Hessian solution algorithms. If the novel Hessian solution algorithm is employed, there is no need to explicitly build the Hessian matrix, if the aim is the solution of the unconstrained MPC problem. The combination of one of the Hessian condensing algorithms with the structure-exploiting Hessian factorization algorithm and the explicit built of the Hessian matrix results in the Riccati-based algorithm originally proposed in [18]. The paper forms the basis of Chapter 9.

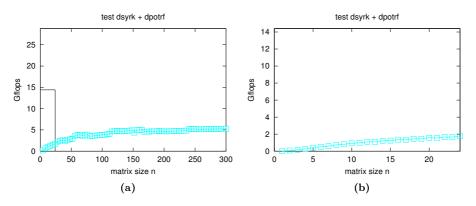

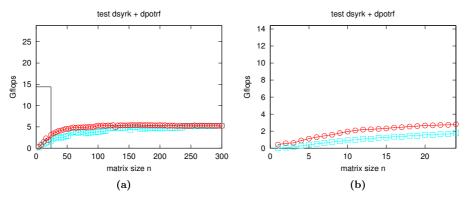

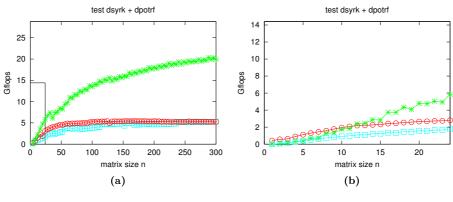

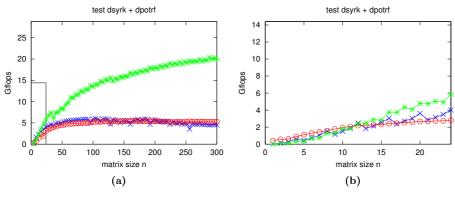

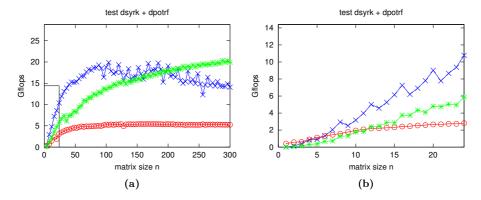

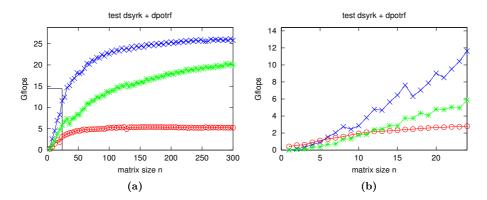

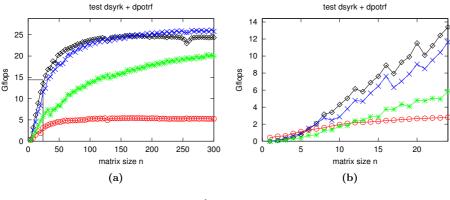

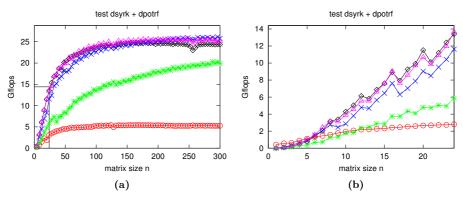

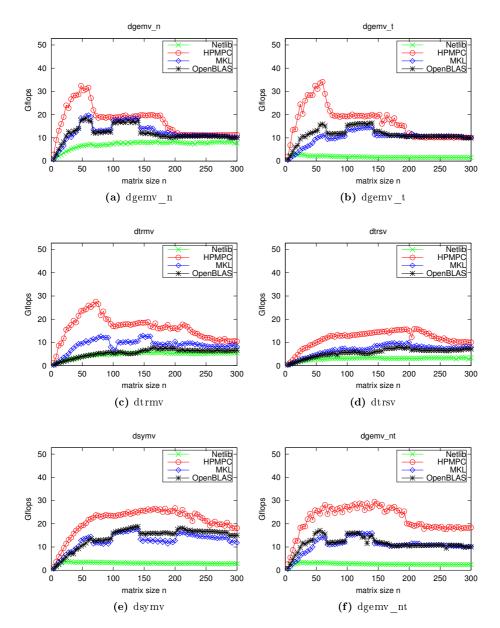

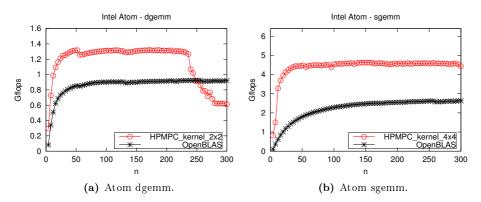

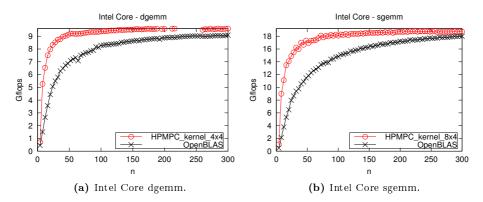

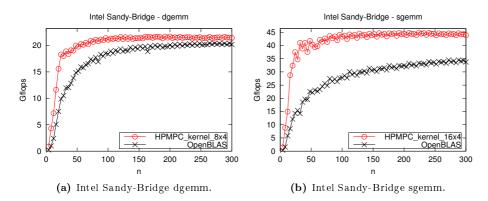

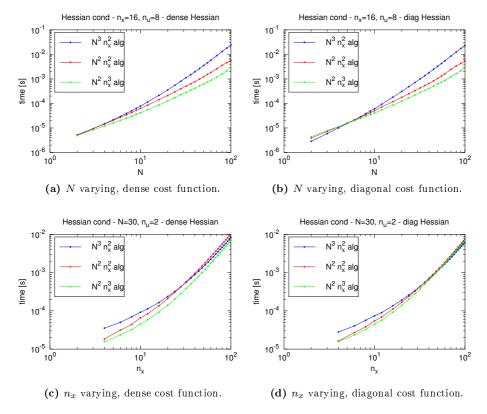

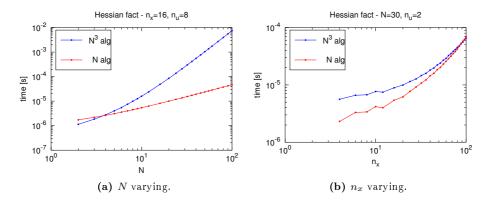

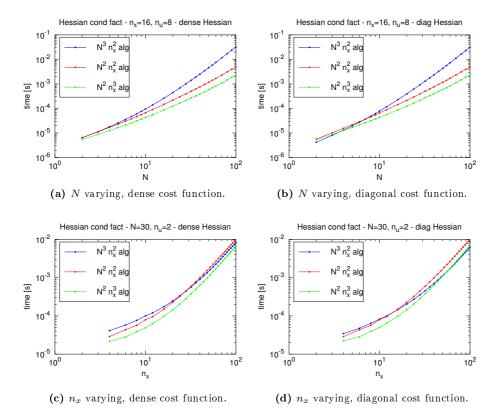

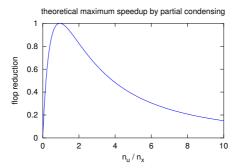

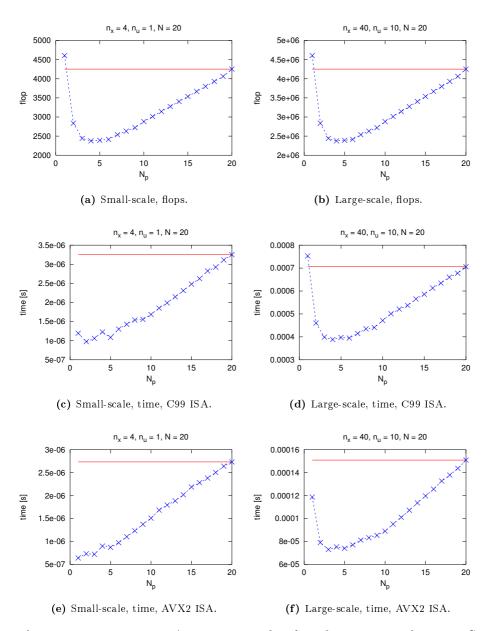

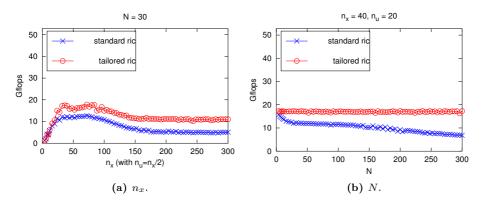

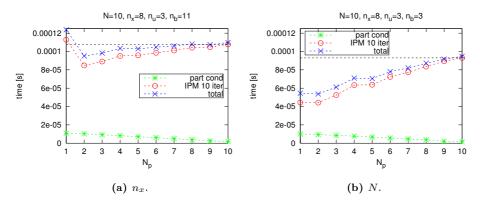

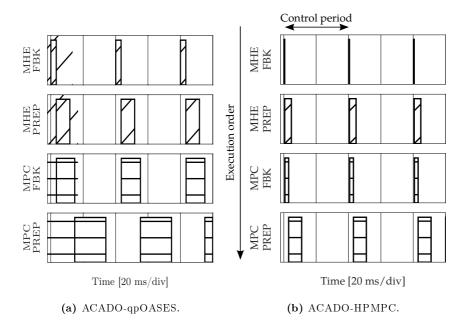

Paper [78] investigates the use of warm-starting to reduce the number of iterations of the Riccati-based homogeneous and self-dual IPM proposed in [76] for the solution of LPs in economic MPC of linear systems. The subject of the paper is no further considered in this thesis.