# Design Optimisation of Fault-Tolerant Event-Triggered Embedded Systems

Jarik Poplavski Kany and Sigurd Hilbert Madsen

Supervisor: Paul Pop

Kongens Lyngby 2007 IMM-M.Sc.-2007-72

Technical University of Denmark Informatics and Mathematical Modelling Building 321, DK-2800 Kongens Lyngby, Denmark Phone +45 45253351, Fax +45 45882673 reception@imm.dtu.dk

# **Abstract**

Computers today are getting smaller and cheaper and are almost everywhere in our daily lives: at our homes, in the cars, airplanes and industry – almost all devices we use contains one or more embedded computers. With growing usage of embedded devices the requirements are getting tighter. In this thesis we address safety-critical embedded systems, where not only the correct result, but also satisfying timing requirements of the system is vital even in the presence of faults.

The increase in computational speed and circuit density has raised the probability of having transient faults. Embedded systems that are used in safety-critical applications must be able to tolerate the increasing number of transient faults. If not, they might lead to failures that would have disastrous consequences and potentially endanger human lives and the environment.

This thesis addresses design optimisation for fault-tolerant event-triggered embedded systems. The hardware of these systems consists of distributed processing elements connected with communication busses. The applications to be run on the hardware are represented by directed acyclic graphs. Processes are scheduled using a fixed-priority preemptive scheduling policy, while messages are transmitted using the Controller Area Network bus protocol. Faults are tolerated for each process through either reexecution or active replication.

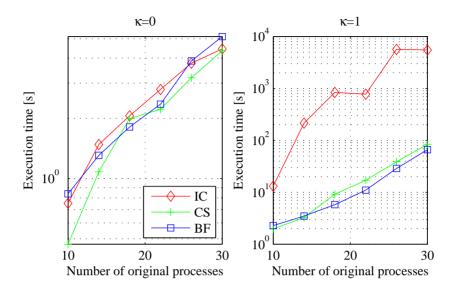

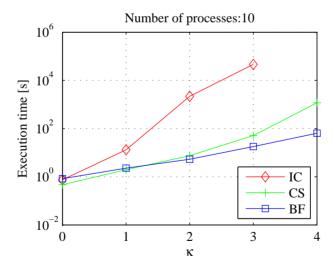

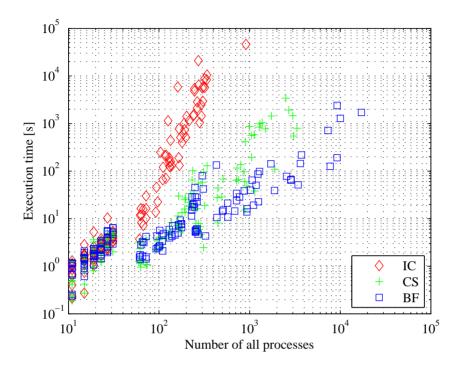

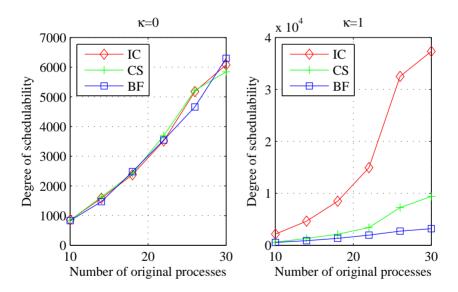

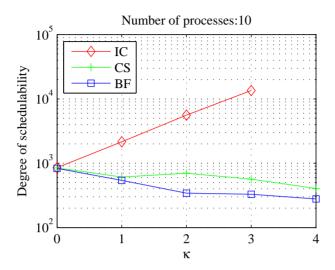

In this thesis we describe a model for representing fault-tolerant applications, called fault-tolerant process graphs (FTPG). We first propose schedulability analysis techniques which can determine whether a fault-tolerant application represented using an FTPG is schedulable. Three different approaches to the schedulability analysis have been proposed: ignoring conditions (IC), condi-

tion separation (CS) and brute force analysis (BF). They differ in the quality of the results and their runtime. Considering the response-time analysis, we also present an optimisation heuristic that decides for each process which fault-tolerance policy to use, and on which processing element to execute it, such that the application is schedulable.

We have evaluated the proposed schedulability analysis and optimisation methods using randomly-generated synthetic applications and a cruise controller application from the automotive industry.

# Resumé

I dag er computere blevet så hurtige, små og billige, at vi nu er begyndt at bruge dem næsten alle steder i vores dagligdag: i hjemmet, i biler, i flyvemaskiner og på fabrikker – stort set alt elektronik indeholder en eller flere indlejrede computere. I takt med den stigende brug af indlejrede systemer vokser også kravet til deres pålidelighed. I denne afhandling adresserer vi sikkerhedskritiske indlejrede systemer, hvor ikke kun det rigtige resultat, men også overholdelse af tidsfristerne, er meget vigtigt, selv når der sker fejl.

Voksende klokfrekvenser og densiteten af digitale kredsløb har medført en øget sandsynlighed for transiente fejl. Indlejrede systemer, som bliver brugt til sikkerhedskritiske opgaver, skal være i stand til at modstå det stigende antal transiente fejl. Alternativt kan det medføre fatale konsekvenser, hvor der vil være fare for tab af menneskeliv eller miljøforurening.

Denne afhandling omhandler designoptimering af sikkerhedskritiske hændelsesstyrede indlejrede systemer. Hardwaren i disse systemer består af distribuerede enheder, som kommunikerer over kommunikationsbusser. Softwaren, som skal afvikles på den givne hardware, er repræsenteret som orienterede acykliske grafer. Processer bliver scheduleret ved brug af faste prioriteter og kan blive preempted af andre processer i applikationen. Beskeder bliver overført ved hjælp af Control Area Network protokol. Fejlene bliver tolereret for hver proces ved hjælp af enten reeksekvering eller replikering.

Vi beskriver en model til at præsentere fejltolerante applikationer – fejltolerante procesgrafer (FTPG). Vi foreslår en responstidsanlyse, som kan afgøre, om en fejltolerant applikation er schedulerbar. Tre forskellige tilgange bliver præsenteret: at ignorere fejlbetingelser (IC), med separering af fejlbetingelser

(CS) og den såkaldte "brute force" analyse (BF). Disse tilgange producerer resultater, som er forskellige både i kvaliteten og i den tid, der er nødvendig for at beregne dem. Baseret på responstidsanalysen, præsenterer vi også en optimerings-heuristik, der for hver process skal finde den optimale fejltoleranceteknik og afgøre på hvilken enhed, processen skal afvikles. Det skal sikre, at applikationen er schedulerbar.

Vi har evalueret de foreslåede responstidsanalyser og optimeringsheuristikken med tilfældigt genererede syntetiske applikationer og en fartpilot-applikation fra bilindustrien.

vi Contents

# **Contents**

| A            | bstra | act                              | i   |

|--------------|-------|----------------------------------|-----|

| $\mathbf{R}$ | esum  | né                               | iii |

| 1            | Intr  | roduction                        | 1   |

|              | 1.1   | Design Flow for Embedded Systems | 3   |

|              | 1.2   | Motivation                       | 5   |

|              | 1.3   | Related Work                     | 6   |

|              | 1.4   | Thesis Objective                 | 7   |

|              | 1.5   | Thesis Overview                  | 9   |

| 2            | Pre   | liminaries                       | 11  |

|              | 2.1   | System Model                     | 11  |

|              | 2.2   | Fault Model                      | 18  |

| 3            | Res   | ponse Time Analysis              | 23  |

viii CONTENTS

|   | 3.1 | Basic WCDOPS+                              | 24  |

|---|-----|--------------------------------------------|-----|

|   | 3.2 | Allowing Several Predecessors              | 33  |

|   | 3.3 | Conditional Analysis                       | 45  |

|   | 3.4 | Pessimism and Performance                  | 51  |

| 4 | Fau | lt-Tolerant Process Graphs                 | 55  |

|   | 4.1 | Definitions                                | 56  |

|   | 4.2 | Data Structures                            | 59  |

|   | 4.3 | Replication                                | 60  |

|   | 4.4 | Reexecution                                | 64  |

|   | 4.5 | Remapping                                  | 73  |

|   | 4.6 | Defining and Seperating Scenarios          | 74  |

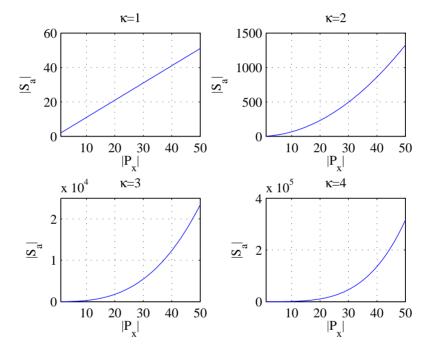

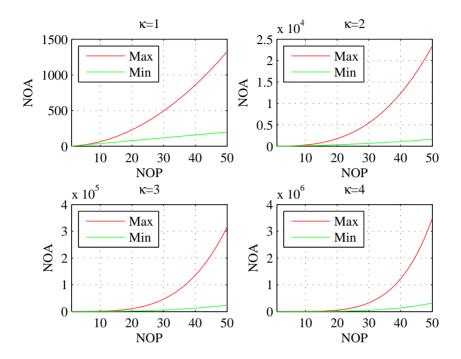

|   | 4.7 | Counting Processes and Scenarios           | 75  |

| 5 | Fau | lt-Tolerance Policy Assignment and Mapping | 79  |

|   | 5.1 | Choosing Priorities                        | 83  |

|   | 5.2 | Choosing Processing Elements for Replicas  | 84  |

|   | 5.3 | Optimizing Policy Mapping                  | 85  |

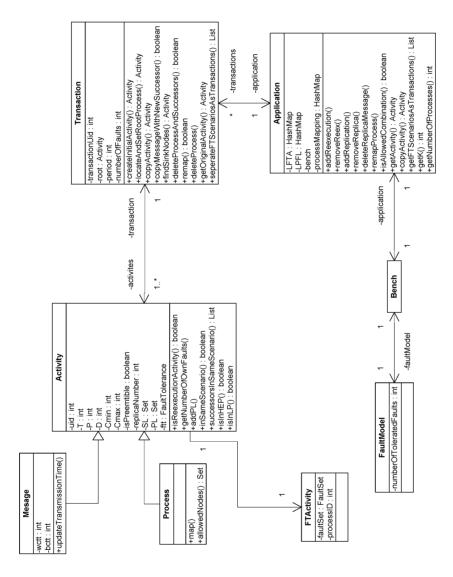

| 6 | Imp | plementation and Testing                   | 95  |

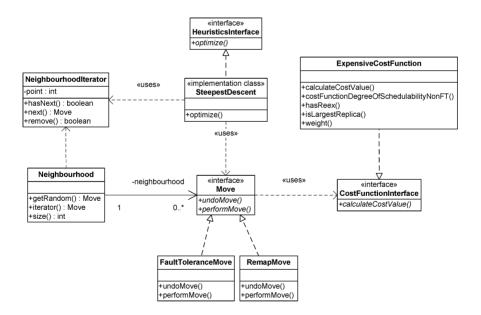

|   | 6.1 | Design Overview                            | 96  |

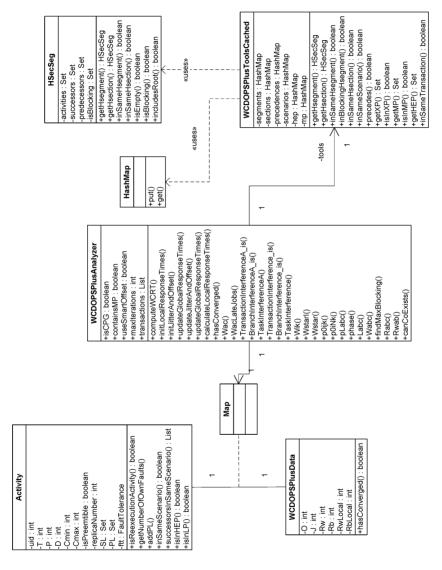

|   | 6.2 | Implementation of WCDOPS++                 | 97  |

|   | 6.3 | Implementation of the Heuristics           | 99  |

|   | 6.4 | Toata                                      | 100 |

| CONTENTS | ix |

|----------|----|

|          |    |

| 7                | Evaluation 10 |                                                       |

|------------------|---------------|-------------------------------------------------------|

|                  | 7.1           | Synthetic Applications                                |

|                  | 7.2           | A Real-Life Example with a Cruise Controller          |

| 8                | Con           | clusions and Future Work 119                          |

|                  | 8.1           | Future Work                                           |

| $\mathbf{A}$     | List          | of Notations 123                                      |

| В                | List          | of Abbreviations 127                                  |

| $\mathbf{C}$     | Pse           | udocode 129                                           |

| D                | Cru           | ise Controller Example 137                            |

|                  | D.1           | Input File for Adaptive Cruise Controller Example 137 |

|                  | D.2           | Results from the Heuristics                           |

| E Other Examples |               | er Examples 141                                       |

|                  | E.1           | Splitting FTPG into Scenarios                         |

|                  | E.2           | LFTA and LPFL                                         |

|                  | E.3           | Calculating Degree of Schedulability                  |

|                  | E.4           | Convergence of the Heuristic                          |

| $\mathbf{F}$     | Prog          | gram 151                                              |

|                  | F.1           | Class Diagrams                                        |

|                  | F.2           | Command Line Manual                                   |

| X        | CONTENTS |

|----------|----------|

| <u> </u> | CONTENTS |

| F.3 XML Schema for Input Files |     |                                                                    |  |

|--------------------------------|-----|--------------------------------------------------------------------|--|

| G Testing 159                  |     |                                                                    |  |

|                                | G.1 | Sanity Checks for Fault Tolerant Conditional Process Graphs $$ 159 |  |

|                                | G.2 | Input for TGFF                                                     |  |

# CHAPTER 1

# Introduction

In the mid 1940s, when the epoch of digital computing started, the first computers were very large and expensive, only available for universities and research centres. Since then, the price and the size of computing systems have been decreasing constantly, and computers become more and more common in our lives. This includes digital watches, CD/DVD players, television, cameras, cell phones, navigation systems, vehicles, aircrafts, and even washers... and many other devices, which we never think of as computers. However, they all do contain a small computer (or many), which is often built for a very specific purpose. We call such computers embedded computer systems.

Comparing to personal computers that can be programmed to perform almost any operation, embedded computers are single purpose devices, often restricted by the needs of the application. The application specific implementation allows embedded systems to be faster, more robust and smaller than general purpose PC, but it also makes them more difficult to design. Not only the required functionality has to be implemented, but also factors like production cost, device size, power consumption, performance and fault-tolerance are to be considered very carefully before starting production.

This project is related to a special class of embedded systems, which are called fault-tolerant embedded systems. Fault-tolerant systems are used for safety-critical applications, where a single fault might lead to catastrophic conse-

2 Introduction

quences, like injuries or loss of human lives and damage to the environment. Such system are typically responsible for critical function control in cars, aircrafts and spacecrafts, nuclear plants, medical devices, etc. They must react to events in the environment within precise time constraints and are therefore called *real-time systems*. Fault-tolerance put very strict requirements on real-time embedded systems, which includes resistance to faults while still meeting any hard deadlines.

Looking at general fault persistence, all faults can be divided into two classes: permanent and transient. Transient faults are induced in hardware, caused by external factors, like radiation particles or lightning stroke that cannot be shielded out. The presence of a transient fault may lead to an error in the application, and this is where the fault-tolerance can be used to save the system from the failure. In this thesis, we address only transient faults.

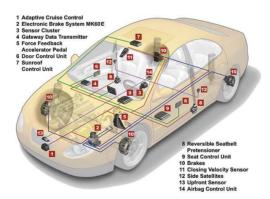

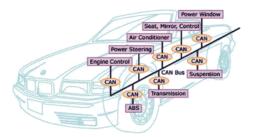

The situation becomes more complex when the system is large and consists of several independent components. Each component is a small embedded computer with CPU, memory and communication capabilities. All components are distributed and interconnected, so they can exchange data in order to work together. We call this type of system a distributed embedded system. An example of a distributed fault-tolerant embedded system can be found in a modern car (see Figure 1.1), which contains a lot of safety-critical components: ABS, cruise controller, airbag system, wheel anti-spin etc.

Figure 1.1: An example of a distributed embedded system [6] with several processing elements and communication busses.

It is the job of the designer to ensure that the embedded system will meet its real-time requirements and produce correct results. As the system can be either time-triggered or event-triggered, the corresponding timing analysis, which checks the

timing requirements, will reflect this. When using a time-triggered model, the schedule is determined at design time. For event-triggered systems a static schedule cannot be produced, since the execution depends on external events arriving during the runtime of the system. Recalling the car example the airbag controller could be an event-triggered system, since it executes its programs in reaction to a "collision" event. This thesis focuses on distributed embedded systems with an event-triggered architecture using bus-based communications.

In the following section we will lay out the general design flow of embedded systems, and show where our work is to be applied. Section 1.2 presents the motivation for the thesis. In Section 1.3 we introduce the related work. In the end of this chapter the reader will find a short overview of the structure of the report. The summarised problem formulation is given in Chapter 1.4.

## 1.1 Design Flow for Embedded Systems

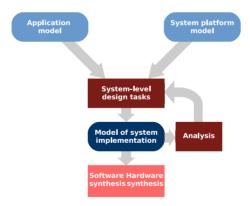

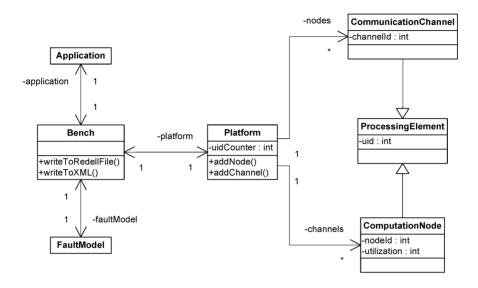

Figure 1.2 shows the system-level design flow for embedded systems. It is based on two inputs, which are the model of the application (software) and the model of the system platform (hardware).

Figure 1.2: The Design Flow for Embedded Systems [30]. This thesis addresses the analysis and the system-level design tasks.

The application model contains processes, including their runtime characteristics, such as deadlines and priorities. The system platform model describes the hardware in the system, which is the embedded devices (computing elements) and the communication channels. The models are used in the stage

4 Introduction

called *system-level design tasks*, and in this work the related tasks can be listed as below:

- Application mapping, this task is about placing the application processes on the different components of the system. For processes it means selecting an appropriate computing element, and for messages it would be selecting communication channels. Some of these mappings might already be decided by the designer.

- Fault-tolerance policy assignment, this task is about selecting an appropriate way of protecting the processes against transient faults. Depending on the constraints, each process will be assigned a fault-tolerance technique, such that the timing requirements are met even in case of faults. We consider reexecution and active replication as the techniques to protect against transient faults.

- Producing a fault-tolerant application is done when all processes have been mapped and assigned a fault-tolerance policy. The result of this task would be a model of system implementation, that describes the execution flow in the system, when transient faults occur. If the produced application satisfies the criteria given by the systems requirements, it can be brought to the next stages.

The tasks above are performed and the results are evaluated in the analysis phase. The analysis of the proposed solution consists of the following parts:

- Schedulability analysis verifies that the application can meet the specified timing constraints. In this thesis, we use a response time analysis, which finds the worst case reponse time and then compares it with the corresponding deadline for each process of the application.

- Performance evaluation measures the overall application performance, which in our case only includes the response times of the processes. But it may also include other factors, like power consumption, CPU/memory utilisation and so on.

The system-level tasks and the analysis are typically done as an iterative process, consisting of generation-evaluation sequences until a satisfactory solution is found.

1.2 Motivation 5

## 1.2 Motivation

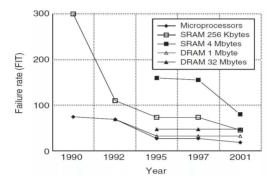

With the improvement of manufactoring techniques, the permanent fault rate of systems is decreasing (see Figure 1.3). On the other hand, the number of transient faults is increasing [9]. Today the rate of transient faults is often very large compared to the rate of permanent faults, the ratio varying from 1:4 to 1:1000 according to [2].

Figure 1.3: Permanent Failure Rates for CMOS Semiconductor Devices [9]

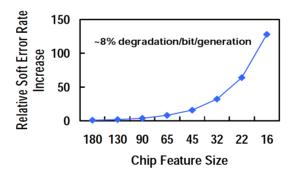

Figure 1.4: Transient Fault Rate Trends [1]

This is, among other things, a result of an increased density of embedded hardware in order to pack more functionality and resources in smaller units. High density leads to increasing electric interference and causes random bit flips. This trend is captured by Figure 1.4. Even in properly designed systems, background radiation and various external electronic magnetic interference will cause transient faults. This problem contradicts the increasing use and dependence on embedded systems, where increasing reliability is a requirement.

6 Introduction

Considering the automotive electronics, modern vehicles are integrating more and more electronic devices for providing better control over the vehicle and improved safety. All modern cars have many built-in embedded systems. Furthermore, automotive manufactures are now designing so-called "control-by-wire" systems. Such systems allow more precise control and better performance. On the other hand, they might loose the tangible safety of mechanical components [10]. It has also been observed that car electronics are often affected by transient faults. The electronics in cars are safety-critical embedded systems, and a proper protection against faults is required in order to avoid fatal consequences.

Traditionally, hardware duplication was used to protect critical components against hardware faults. In case of a failure the correctly working components would ensure the stability of the system. Unfortunately this solution is a very costly way of treating transient faults that occur and disappear randomly. And the manufactures need to look at the alternatives, like reexecution and software replication. However, applying reexecution or replication may and probably will introduce significant timing delays in the system, and the designer can possibly end up with a solution that is not schedulable. Therefore, designers may need an optimisation technique that can help them to introduce redundancy in the most cost-efficient way.

## 1.3 Related Work

Hardware redundancy is a common way of tolerating single permanent faults, and it has been used in a number of fault-tolerant arcitectures, such as MARS[27], TTA[26] and XBW[7]. Hardware redundancy can also be used to protect the components of a system against transient fault, but often such a solution is very impractical due to high cost of the hardware.

There has been academical research that addresses modelling and scheduling of processes on distributed multiprocessor systems [13, 31, 16]. However, many of these assume that the processes are independent, which is not the case in the real world. Processes in an application can have both data and control dependencies. They might need to exchange intermediate results across different platforms and communicate through a medium. The knowledge about process dependencies can be used to improve the accuracy of the response time analysis (RTA). There have been proposed algorithms that can take inter-process dependencies into account [39, 41, 19, 8, 17]. They are all based on the concepts of offset, jitters and phases, which are used to model the time intervals between releases of processes.

Tindell introduced a technique in [39] to compute worst-case response time by using static offsets, and his analysis was later extended and improved in [20] by Palencia and Harbour. In the last paper they developed a better elimination of precedence conflicts and introduced analysis of processes that belong to the same sequence during the execution. The result was a reduced pessimism of the RTA. Their algorithms were called WCDO¹ [19] and WCDOPS² [20]. More recently work has been done by Redell, who developed a newer version of the response time analysis with precedence constraints based on the WCDOPS algorithm. Redells algorithm, called WCDOPS+, reuses and improves the concepts defined in [20], which makes it applicable to systems with both preemptive and non-preemptive schedulers. This algorithm has been chosen as the starting point for the response time analysis in this thesis. We also propose several improvements related to precedence and fault conditions.

Different ways of handling both transient and permanent faults have been proposed. Xie et al. in [22] describe an allocation and scheduling algorithm to handle transient faults with replication of critical processes. Very few researchers [21, 29] consider the optimization of implementations to reduce the impact due to fault-tolerance on performance and, even if optimization is considered, it is very limited and does not include the concurrent usage of several redundancy techniques. In [23], Izosimov presents several design optimisation strategies for applying fault-tolerance in embedded systems. More recently Pop et al. propose in [14] a design optimisation approach for statically scheduled applications, using active replication and reexecution as fault tolerance techniques.

## 1.4 Thesis Objective

The objective of this thesis is to develop and evaluate a design optimisation technique for fault-tolerant embedded systems. We focus on the automatic assignment of fault-tolerance and mapping that protect the system against a fixed number of transient faults while obeying the real-time requirements.

An embedded system in this thesis is described by an application, a hardware architecture and a fault model. The application is a set of processes with possible control and data dependencies. Cyclic dependencies are not allowed. Data dependencies are messages having a sending and a receiving process. A group of processes with mutual dependencies is called a transaction with a period representing the minimum interval between events triggering the transaction.

<sup>&</sup>lt;sup>1</sup>Worst Case Dynamic Offsets

<sup>&</sup>lt;sup>2</sup>Worst Case Dynamic Offsets with Priority Schemes

8 Introduction

The hardware architecture is distributed and consists of one or more processing elements and possible a number of communication busses. We assume that the scheduling on the processing elements is event-driven, preemptive with fixed priorities, while messages are non-preemptive with fixed priorities and transmitted using a CAN bus. The application contains a mapping table that defines on which processing elements each process can execute. If a process is allowed to run a given processing element, the corresponding best and worst case execution time must be given. The designer must also assign a fixed priority to each process as well as the initial mapping. Messages are statically allocated by the designer to a communication bus. Best and worst case transmission time as well as priority must also be given. Deadlines of processes and messages must be given by the designer and they are always hard. It is assumed that all bounds on execution and transmission time are known prior to the analysis.

The fault model describes how many transitient faults are allowed in every period of the application. In order to tolerate faults, two different approaches are used: reexecution and replication. The dilemma is that both techniques increase the utilisation of computational resources and hence may break real-time requirements to the system.

Therefore, the goals for this project can be stated as following:

- Provide a modelling framework that can represent the system and model the faults.

- Provide a reliable response time analysis that can be used to validate whether the system obeys the timing constraints when considering a fixed number of transitient faults.

- Provide a heuristic algorithm for optimising fault-tolerance assignment and mapping.

- Evaluate and elaborate the proposed methods with synthetically generated systems.

- Evaluate an example from the real world, an adaptive cruise controller.

However, a number of assumptions has been done in the following analysis. These assumptions are basically simplifications of the model:

• The communication system is assumed to be fault-tolerant that is to say we do not protect the messages against transmission errors.

- The overheads related to the system environment are neglected. It means that there are no other applications running on the processing elements except for the one being analysed.

- The operating system is transparent in sense that all overheads are included in the execution times of the processes

- Deadlines of processes must be shorter than the period of the transaction

- When doing reponse time analysis of fault-tolerant process graphs, only one transaction is allowed

## 1.5 Thesis Overview

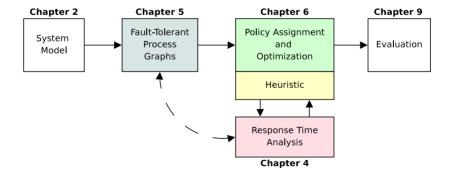

In the following we will briefly present the different parts of this thesis and explain the relations between the corresponding chapters. We have divided the thesis into a number of sub problems as shown Figure 1.5. The arrows in the figure are used to illustrate the relations between the defined sub problems.

To begin with, all necessary basic theoretical concepts will be explained in Chapter 2. This preliminary chapter contains an introduction to the hardware, application and fault models used in the thesis, presents fault tolerance techniques and the basics of scheduling.

Figure 1.5: Thesis Guideline Diagram

Chapter 3 addresses the response time analysis. It contains a description of the existing WCDOP+ algorithm, including all necessary details to understand how

10 Introduction

it works. Besides that, the chapter includes a complete description of the extensions proposed to the algorithm. Chapter 4 deals with fault-tolerant process graphs and covers the basic notation and definition of elements. It describes the data structures and necessary transformations applied when changing between different fault-tolerance techniques and mappings.

Chapter 5 is entirely dedicated to the fault-tolerance assignment and optimisation. It explains how to choose the most optimal policy assignment using the response time analysis described before. With this theoretical foundation in place, we give some details on our implementation in Chapter 6 including data structures, relations between equations and methods, and the pseudocode for some of the operations on our data structures. The optimisations we have done to improve the performance of the program will also be discussed. In this chapter we will also explain our approach to testing, which includes both unit tests and functional tests.

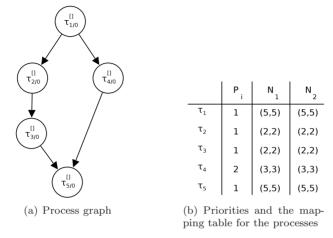

In Chapter 7 an extensive evaluation of our algorithm will be performed and discussed. These evaluations are done on numerous synthetic applications and a cruise controller example from the automotive industry. We summarise and make conclusions on the work in relation to the obtained results in Chapter 8. Based on our work, suggestions for future work are listed and discussed in Section 8.1.

Notice that Appendicies A and B contain lists of abbreviations and notations, respectively, that will be used throughout the report.

# Chapter 2

# **Preliminaries**

In this chapter we will lay out the preliminaries for the thesis. This includes notations, model description and an introduction to fault tolerance related to this thesis. In Section 2.1 we give a comprehensive description of the system model, which includes both description of the hardware and the software architectures. Section 2.2 describes faults in the given context and presents several related fault-tolerance techniques, including process replication and reexecution.

## 2.1 System Model

This section explains the system model, which includes the hardware platform and application model, i.e. the software to be executed on the hardware platform.

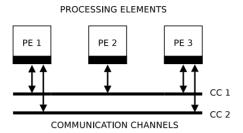

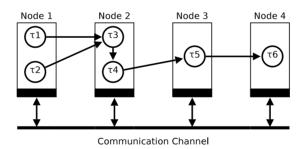

#### 2.1.1 Hardware Architecture

The hardware architecture of the embedded system is composed of a set of processing elements, which are distributed and interconnected by one or more communication channels, see Figure 2.1. Each processing element consists of a

12 Preliminaries

CPU, memory and a communication subsystem. The communication system is responsible for low-level operations, such as communication protocols and error correction during communication.

Figure 2.1: A View of the Hardware Architecture. The shown system contains three processing elements connected by two communication channels.

In the thesis we handle all subsystems on the processing elements as a whole, regardless of any overheads that may be introduced by interaction between different hardware levels. The size of communication buffers and memory are, for simplicity, not considered.

The messaging subsystem contains an arbitrary number of communication channels that are used to deliver messages between the processes. There exists a number of busses and protocols for transferring data between the processes. Some are general purpose while others are specific for a particular industry. As we are only considering event-triggered systems and since the project relates to the automotive industry, we have assumed that Controller Area Network (CAN) is used for the communication. We make the simplification and assume that no faults will happen during communication or they will be tolerated using existing techniques. Figure 2.2 shows a CAN bus connecting different subsystems in a modern car.

Messages being sent over the CAN are not preemptive. Once the transmission of a given message has started, other processing elements cannot start a new transfer before the transmission has finished. This also implies that only a single message can be transmitted at any given time on a particular communication channel. However, since CAN defines message content rather than message destination, the same message will be received by all processing elements on the bus. The messages do also have priorities that can be used to determine what message to send, if more than one message are ready to be sent. This is implemented by the arbitration field of the CAN frames.

Figure 2.2: An example of a Controller Area Network (CAN) in a car [11] where different components are connected through the bus.

If two processes are mapped on the same processing element, then the transmission time of a message is neglected. In this case the message will be placed directly into the shared memory, when the sending process finishes. In a situation when the sending and receiving processes are not on the same processing element the message will be sent through the communication channel.

#### 2.1.2 Software Architecture

The software architecture used on the top of the hardware is a real-time operating system (RTOS), which can perform in such a way that all timing requirements are satisfied. As we are only interested in the real-time properties of the RTOS, all other details are omitted being irrelevant.

The execution model is based on real-time preemptive scheduling with fixed priorities. It means that the RTOS can switch between processes, and processes having higher priorities will interrupt execution of lower priority processes. When it happens, the lower priority process has to wait until the high priority process finishes its execution. Priorities are related to the process importance, and are given by the designer. Preemption can happen at any point of time, as it depends on the priorities of the processes and even arrivals.

14 Preliminaries

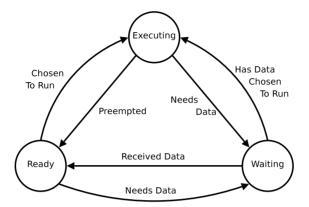

Figure 2.3: Scheduling States of a Process. The diagram shows how the RTOS controls the execution of a process.

The scheduling states of a process follow the scheme proposed at [40] and is shown in Figure 2.3. If several processes are active, i.e. ready to be run, the schedule will always choose the one with the highest priority. If those processes have the same priority, the choice will be non-deterministic.

Generalisation of the RTOS running on top of each processing element is done with the assumption that the following overheads are included in the worst case execution time of the processes:

- Context switch and process activation.

- Error detection.

- Recovering of process inputs.

- Interaction with the communication layer.

We also assume that some synchronisation takes place between the processing elements achived through message transmissions. It is simply assumed that the mechanism is given and does not introduce any overhead.

## 2.1.3 Application Model

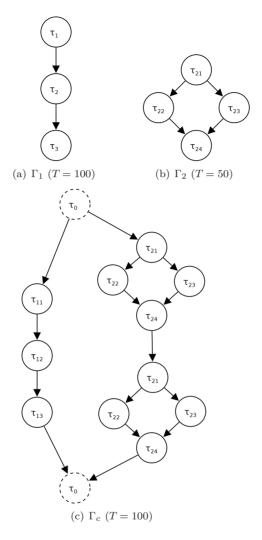

The application model describes a set of processes that together form an application, denoted  $A_i$ . An application is represented as a set of acyclic directed

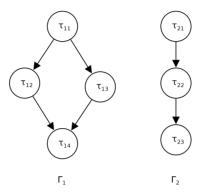

graphs,  $A_i = \Gamma_a(\mathcal{V}, \mathcal{E})$ . An example is shown in Figure 2.4.

Figure 2.4: An Example of an Application Consisting of Two Transactions

A graph  $\Gamma_a$  is also called a transaction or process graph and has a period  $T_a$ . Each vertex  $\tau_a \in \mathcal{V}$  in the graph  $\Gamma_a$  represents a process, and each edge  $e_{ij} \in \mathcal{E}$  from  $\tau_i$  to  $\tau_j$  represents a precedence constraint between two processes. By using precedence constraints we can model the order of execution of the processes in an application. It means that a process having precedence constraints from other processes, cannot be executed before all of those processes have finished even if it has a higher priority. A transaction therefore groups processes that have precedence constraints. A process that have no precedence constraints is called the root process.

Each precedence constraint between two processes may have an associated mes-sage,  $m_i$ , sent through one of the communication channels. In this case, the

precedence relation is called a data dependency. A message is only transferred

when the sending process has finished, and the receiving process cannot start

its execution before the message has been completely received.

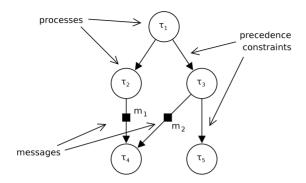

Figure 2.5 shows a single transaction consisting of five processes ( $\tau_1$ , ...,  $\tau_5$ ), illustrating the graph representation of an application. In the figure, the precedence constraints are drawn as edges without messages, whereas the messages are drawn using boxes  $m_1$  and  $m_2$  on the edges.

16 Preliminaries

Figure 2.5: An Example of a Process Graph. The arrows show the elements of the graph.

A process is described by a set of temporal and execution properties, given in Table 2.1.

| Notation | Short Description                |

|----------|----------------------------------|

| $C_a$    | Worst Case Execution Time (WCET) |

| $C_a^b$  | Best Case Execution Time (BCET)  |

| $P_a$    | Priority Deadline                |

| $D_a$    | Deadline                         |

| $T_i$    | Period                           |

Table 2.1: Properties of a Process

The execution times are the lower and upper bounds of time required for a process to complete. In the model, execution time depends on the chosen processing element. Therefore the execution times are given as a table, where each pair of process and processing element is represented by best and worst case execution times. Such a table is called a *mapping table* and an example is given in Table 2.2. If a mapping is not allowed, the corresponding entry in the table is empty. In Table 2.2, process  $\tau_2$  is not allowed to execute on processing element  $N_2$ .

|          | $N_1$ | $N_2$  |

|----------|-------|--------|

| $\tau_1$ | (1,2) | (2,3)  |

| $\tau_2$ | (7,7) |        |

| $\tau_3$ | (6,9) | (7,10) |

Table 2.2: Example of a mapping table from a system model containing the best- and worst case execution time for the processes on the different processing elements.

The priority indicates the importance of the process – higher numbers mean higher priority, so the execution of low priority processes may be preempted by higher priority processes. The deadline is the latest point in time, at which the process is supposed to have finished executing. In real-time systems with hard deadlines all processes must successfully complete before their deadlines. In this model, the deadlines are absolute, meaning that the time is counted from the arrival of the event triggering the execution. The period of the transaction represents the minimum interval of time between any two events causing activation of the transaction. Deadlines are not allowed to be longer than the period of the transaction. Because of the precedence relations defined by the transaction, the period for all processes in the given transaction must be equal to the period of the transaction.

Similarly to processes, messages are characterised by the following properties:

| Notation   | Short Description                   |

|------------|-------------------------------------|

| $C_i^m$    | Worst Case Transmission Time (WCTT) |

| $C_i^{mb}$ | Best Case Transmission Time (BCTT)  |

| $P_i^m$    | Priority                            |

| $D_{ij}^m$ | Deadline                            |

Table 2.3: The properties of a message.

All messages are statically assigned to a communication channel, and this cannot be changed during the design optimisation.

18 Preliminaries

#### 2.2 Fault Model

As mentioned in the previous sections, we do not look at the fault detection. We assume that the RTOS contains a mechanism to detect the faults and notify the scheduler. The time needed for the detection of an error is called error detection overhead, and the time needed for the system to restore the initial state of the process is called recovery overhead. We have assumed that these overheads are included into process execution times, and state recovering takes no time. We denote the maximum number of transient faults that might happen during one period of the transaction as  $\kappa$ .

When a fault occurs, we always assume that it happens at the worst possible instant in time. This is exactly when the process is about to finish, thereby introducing the maximum delay for subsequent processes.

We are now going to present two fault-tolerance techniques, which are relevant for our model. These are reexecution and replication, which are the most used techniques for tolerating transient faults. Notice that a process can only be protected by one of the two techniques.

#### 2.2.1 Process Reexecution

Reexecution provides fault-tolerance by running a process a second time on the same processing element if it fails. Indeed the reexecution may be one of the natural ways of dealing with faults - if something did not work, then try one more time. The use of reexecution may be unsuitable in some situations, because the successful completetion will be significantly delayed.

Figure 2.6: An Example of Reexecution. Process  $\tau_{1/2}$  is only run, when process  $\tau_1$  fails.

Consider Figure 2.6 where process  $\tau_1$  fails and is reexecuted. The  $j^{th}$  execution of a process is denoted by slash in subscript, so the first execution is written as  $\tau_{1/1}$  and the first reexecution is written as  $\tau_{1/2}$ . The set of processes protected with reexecution is denoted  $\mathcal{P}_x$ . The reexecution approach has the advantage that it is simple to implement. On the other hand the reexecution approach may

2.2 Fault Model 19

prolong the response time of the faulty process and thus may result in missed deadlines.

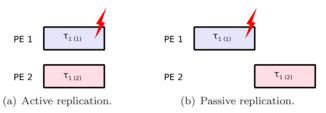

## 2.2.2 Process Replication

Another way of protecting processes against faults is to use process replication. Compared to the reexecution, which is based on time redundancy, the replication approach uses space redundancy. When using active replication, several instances of the same process, called replicas, are executed in parallel on different processing elements independently of fault occurrences. With passive replication, replicas will only start, if the primary process fails. Both methods are illustrated in Figure 2.7. In our thesis we focus only on active replication.

Figure 2.7: Two Types of Process Replication.

We denote replication with round brackets in subscripts surrounding the replica number, j. For the main process the replica number is always zero, and its replicas will have consecutive numbers starting from one. In the figure above the primary process is denoted as  $\tau_{1(0)}$ , and its replica is  $\tau_{1(1)}$ . The set of processes that are protected with replication, is denoted  $\mathcal{P}_r$ .

The main advantage of active replication is that a transient fault does not delay the response time of the protected process as much as with reexecution in most situations. On the other hand, the system will also have to execute the replicated process if no faults occur at all, and therefore consume more resources.

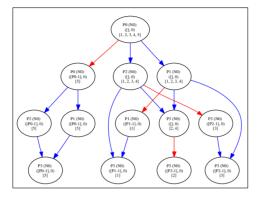

## 2.2.3 Fault-Tolerant Process Graph

In order to model fault occurrences in our system we use conditional process graphs (FTPG), denoted  $\mathcal{G}_a$ . A conditional process graph is similar to a regular process graph, extended by adding guards on the edges to model fault

20 Preliminaries

occurences. The guards are boolean conditions indicating the presence of a fault.

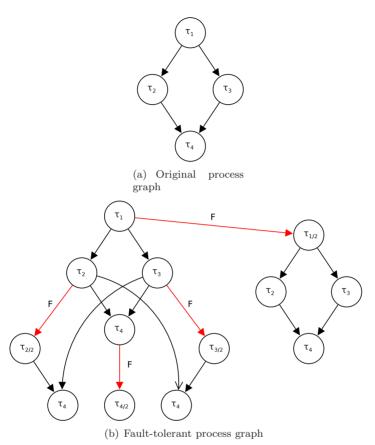

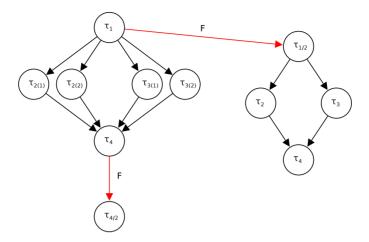

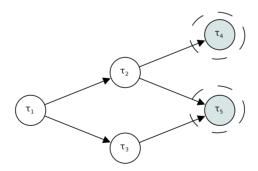

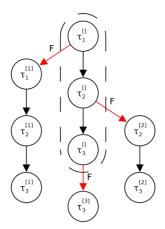

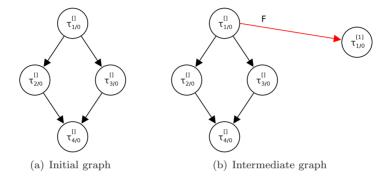

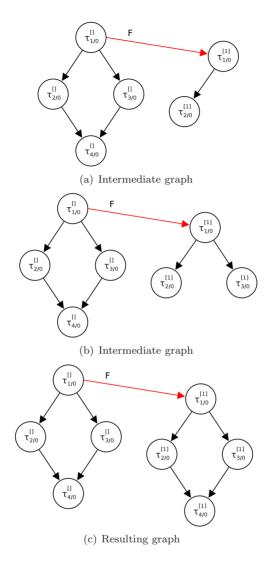

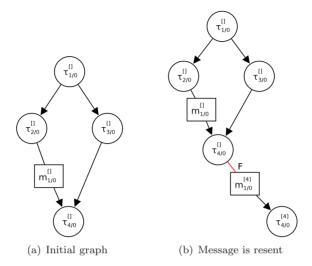

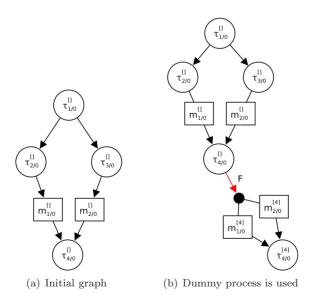

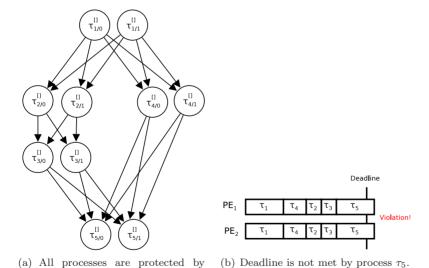

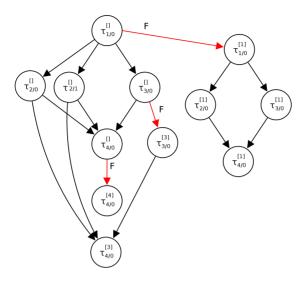

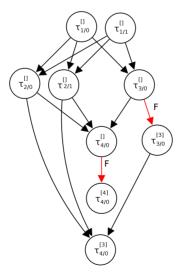

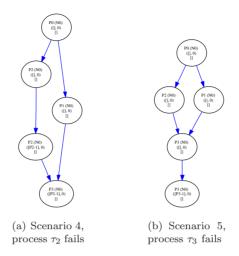

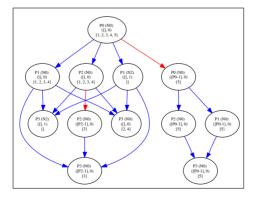

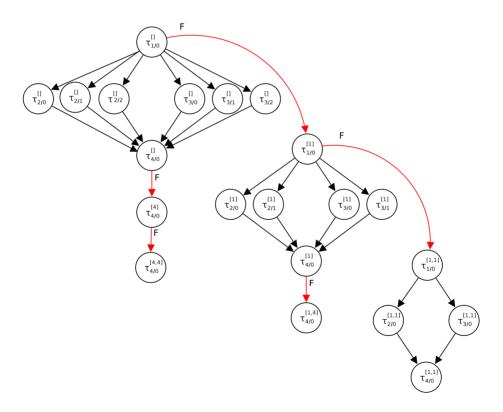

Figure 2.8: Producing Fault-Tolerant Process Graph with All Processes Being Reexecuted.

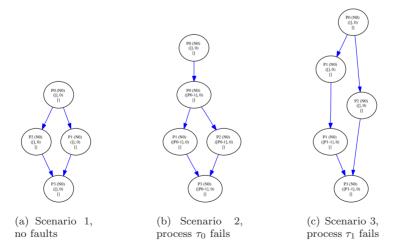

Figure 2.8(a) demonstrates a process graph, that has been extended to a fault-tolerant process graph in Figure 2.8(b). All processes are set to be reexecuted in case of faults, and the maximum number of tolerated faults  $\kappa$  is 1. Depending on the presence of fault for a process, the corresponding edge must be taken. If a process finishes successfully, then all non-faulty edges must be taken. If the process fails, then it must be reexecuted and therefore the execution path will include the conditional edge, F, starting at the faulty process. The fault and non-fault conditions are mutually exclusive for a given process, and only one type can be taken during the execution.

2.2 Fault Model 21

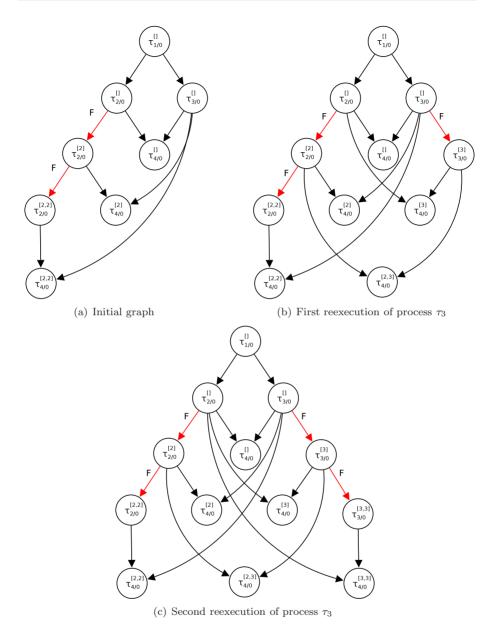

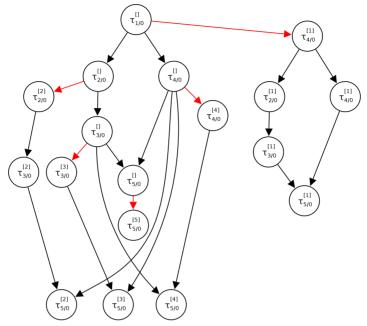

Figure 2.9: Combining Reexecution and Replication. Processes  $\tau_2$  and  $\tau_3$  are replicated, while processes  $\tau_1$  and  $\tau_4$  are reexecuted

Figure 2.9 shows how the reexecution and the replication can be combined when  $\kappa=1$ . The shown graph represents a fault-tolerance policy assignment by which processes  $\tau_1$  and  $\tau_4$  are chosen to be reexecuted, and processes  $\tau_2$  and  $\tau_3$  are protected with active replication. It should be noted, that if process  $\tau_1$  fails and is reexecuted as  $\tau_{1/2}$ , the succeeding processes will not experience any faults (recall that  $\kappa=1$ ). It leads to removal of replicas  $\tau_{2(2)}$ ,  $\tau_{3(2)}$  and reexecution  $\tau_{4/2}$  from the fault-scenario started by the fault in  $\tau_1$ .

As mentioned earlier, we do not combine the reexecution and replication for the same process. When using replication, we always assume no faults have occured during the execution of the replicas. Therefore we need to protect succeeding processes against the same number of faults as the process being replicated. In contrast, reexecution captures the presence of a fault, and the succeeding processes must be protected against  $\kappa-1$  faults.

A specific trace or execution path through an FTPG for a certain combination of faults captured, is called a *fault scenario* and is denoted  $s_{is}$ . Any FTPG will always have at least one fault scenario - the situation with no faults. The set of all fault scenarios for a given FTPG,  $S_i = \{ \forall s_{is} \in \mathcal{G}_i \}$ , represents all possible combinations of faults that can be captured. It includes also situations with less than  $\kappa$  faults.

We now have presented the basic terminology and the models that will be used through this thesis. On this foundation, we will define the objective of this 22 Preliminaries

thesis more closely in the following chapter.

# Chapter 3

# **Response Time Analysis**

In this chapter we present the response time analysis algorithm for event-triggered systems, WCDOPS+, which we use as a starting point for our schedulability analysis. The original version was developed by Ola Redell and described in his works [35, 34]. We have extended the WCDOPS+ in order to deal with fault-tolerant scheduling. The basic idea of response time analysis (RTA) is to determine the worst-case response times of all processes. By comparing the worst case response times with the deadlines, we can test the schedulability of the system.

The chapter is structured as follows. Section 3.1 explains the approach used in WCDOPS+ and introduces the theoretical background required to understand how the algorithm works. Then we will present our extensions to the algorithm in Section 3.2, and explain how the algorithm can be applied on fault-tolerant applications in Section 3.3.

Details on the implementation of the algorithm are described in Chapter 6.

## 3.1 Basic WCDOPS+

In this section we will describe the basic WCDOPS+ analysis as given in [34]. All equations, unless otherwise stated, are taken from [34].

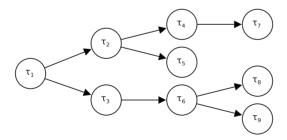

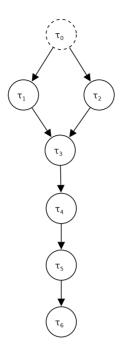

The WCDOPS+ algorithm allows us to perform response time analysis on distributed event-triggered systems. The processes are grouped into transactions. The execution of a transaction,  $\Gamma_i$ , is triggered by an external event. The events arrive aperiodically with a minimum interval between the releases denoted by  $T_i$ . Each transaction contains a set of processes having precedence, which form a tree-shaped acyclic graph, as shown in Figure 3.1. An activation of the transaction  $\Gamma_i$  is called a *job*, implying that all processes of the transaction will belong to the same job for the arrival of a given event.

The processes are identified by two subscripts: an unique number among other processes in the same transaction and the number of transaction, they belong to. A transaction has only *one* root process, and in Figure 3.1 the root process is  $\tau_1$ . The processes are mapped on different processing elements, and the mapping is given by  $\mathcal{M}(\tau_{ij})$ . The priority of a process is denoted by  $P_{ij}$ . For the best case response time of a process  $\tau_i$  we use the notation  $R_i^b$ , and the worst case response time is denoted by  $R_i^w$ .

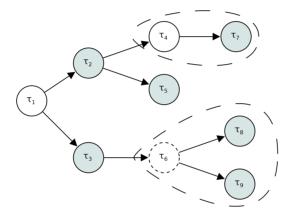

Figure 3.1: An Example of a Tree-Shaped Transaction with Nine Processes

## 3.1.1 Modelling Precedence Relations

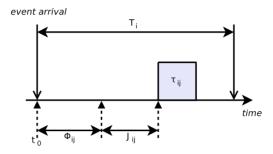

The precedence relations are expressed by offsets and jitters, which help to model processes with precedence as they were independent. An offset,  $\Phi_{ij}$ , is the minimum relative time after an event has arrived to the activation of process  $\tau_{ij}$ . The offset is then the earliest possible instant at which a process can start

executing. The jitter,  $J_{ij}$ , is the maximum delay that a process can experience from its earliest possible arrival until it is released. Then, if the event arrives at time  $t_0$ , the latest point in time process  $\tau_{ij}$  can be released, is given by  $t_0+\Phi_{ij}+J_{ij}$ . Figure 3.2 illustrates the relation between the arrival of the event and the execution of process  $\tau_{ij}$ .

Figure 3.2: Offset and Jitter Relation

Offsets and jitters are dynamically updated between the iterations of the algorithm as follows:

$$\Phi_{ij} = R_{ip}^b \tag{3.1}$$

$$J_{ij} = max(R_{ip}^{w} - R_{ip}^{b}, J_{ip})$$

(3.2)

The equations show that the offset is found as the best case response time of the preceding process  $\tau_{ip}$ , and the jitter is the difference between worst case and best case response times of the preceding process.

The WCDOPS+ algorithm will find best case and worst case response times for each process in the system. The particular process, which is currently being analysed, is denoted as  $\tau_{ab}$ . The main idea behind the analysis is to find the maximum possible interference from other processes in the system, that may delay the execution of process  $\tau_{ab}$  either due to preemption or precedence relation. The maximum interference is found by analysing the busy period of  $\tau_{ab}$ . The busy period is the period, when the processor on which  $\tau_{ab}$  is mapped, is occupied by other processes having the same or higher priority as  $\tau_{ab}$ . This implies that the execution of  $\tau_{ab}$  will be preempted by these processes. The set of processes that run on the same processing element as  $\tau_{ab}$  and having equal or higher priority is given by  $hp_i(\tau_{ab})$ . Consequently  $lp_i(\tau_{ab})$  represents the set of lower-priority processes. Formally  $hp_i(\tau_{ab})$  is defined as

$$hp_i(\tau_{ab}) = \{ \tau_{ik} \in \Gamma_i \mid P_{ik} \ge P_{ab} \land \mathcal{M}(\tau_{ij}) = \mathcal{M}(\tau_{ab}) \}$$

(3.3)

and  $lp_i(\tau_{ab})$  is given by

$$lp_i(\tau_{ab}) = \{ \tau_{ik} \in \Gamma_i \mid P_{ik} < P_{ab} \land \mathcal{M}(\tau_{ij}) = \mathcal{M}(\tau_{ab}) \}$$

(3.4)

These are very important definitions and will be used extensively through the analysis.

#### 3.1.2 Process Phasing

The busy period of  $\tau_{ab}$  starts at some point of time, called the *critical instant*  $t_c$ . The worst case delay for  $\tau_{ab}$  will be created, when processes in  $hp_i(\tau_{ab})$  are phased in such a way that they are released at  $t_c$ . In this situation, the execution of  $\tau_{ab}$  will be delayed the most due to these higher-priority processes. The algorithm also takes into account the interference from other transactions in the application, that might have different periods, than the transaction to which  $\tau_{ab}$  belongs. The maximum contribution to  $\tau_{ab}$  busy period from a given transaction  $\Gamma_i$  happens when a process  $\tau_{ik}$  in  $hp_i(\tau_{ab})$  originating from  $\Gamma_i$  starts the busy period. However, in case when deadlines are larger than event periods, the interference can also occur from previous jobs of the same transaction.

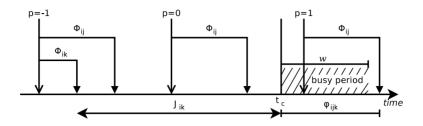

In order to find the maximum contribution from a particular transaction  $\Gamma_i$ , the algorithm must identify all processes from all jobs of the transaction that are ready to be executed in the busy period. To identify all pending instances of a process  $\tau_{ij}$  a phase relation  $\varphi_{ijk}$  between  $\tau_{ij}$  and  $\tau_{ik}$  is used to find the earliest possible arrival of process  $\tau_{ij}$  after  $t_c$ . The phase is defined as

$$\varphi_{ijk} = T_i - \Phi_{ij} - (\Phi_{ik} + J_{ik}) \bmod T_i \tag{3.5}$$

and the total number of pending instances  $n_{ijk}$  of process  $\tau_{ij}$  at  $t_c$  is

$$n_{ijk} = \left| \frac{J_{ij} + \varphi_{ijk}}{T_i} \right| \tag{3.6}$$

The jobs and the corresponding instances of processes are assigned an index p, based on the arrival time of the external event relative to  $t_c$ . The positive values are assigned to instances coming after  $t_c$ , whereas  $0^{th}$  and negative indexes indicates that the job arrives prior to  $t_c$ . The phase relation and numbering of pending jobs is illustrated in Figure 3.3.

Figure 3.3: Job Numbering and Phasing for Process  $\tau_{ij}$  relative to  $t_c$

The width of the busy period started by  $\tau_{ik}$  at  $t_c$  is given by w, and the contribution from a process  $\tau_{ij}$  is only possible, if the processes are phased in such a way, that  $\tau_{ij}$  is released during w. In Figure 3.3 the number of pending instances  $n_{ijk}$  of  $\tau_{ij}$  is therefore 2, with indexes p=1 and p=0. The latest instance has always index p=0, and thus the index p of the first pending instance of  $\tau_{ij}$  can be found as

$$p_{0,ijk} = 1 - n_{ijk} = 1 - \left| \frac{J_{ij} + \varphi_{ijk}}{T_i} \right|$$

(3.7)

which in our case is p = -1, i.e. triggered by the earliest event arrival.

## 3.1.3 Process Grouping

Another important concept, which is presented in the WCDOPS+ algorithm, is grouping of processes in H-sections and H-segments. Sections and segments consist of many processes, that due to their priorities and precedence relations can be treated as a single large process. They are used in the analysis, since they group processes that may belong to the same busy period of process  $\tau_{ab}$ . Segments and sections are always determined relative to a given process, which in our case is  $\tau_{ab}$ . The priority and mapping of  $\tau_{ab}$  is used to check whether two processes are in the same segment or section. The definition of an H-segment is given as follows:

$$H_{ij}^{seg}(\tau_{ab}) = \{ \tau_{ij} \in hp_i(\tau_{ab}) \mid (\neg \exists \tau_{il} \in \Gamma_{ij} \Delta \Gamma_{ik} \mid \tau_{il} \notin hp_i(\tau_{ab})) \}$$

(3.8)

Two processes that are in  $hp_i(\tau_{ab})$  belong to the same segment, if there is no other processes  $\tau_{ij} \notin hp_i(\tau_{ab})$ , that precedes one process but not the other process. In other words, the processes in a segment may not contain any intermediate processes that are not in  $hp_i(\tau_{ab})$ . The main property of an H-segment is that if one process from the segment belongs to the busy period, then all processes in the segment will contribute to the busy period, and this is why a

segment may be considered as a single large process. In contrast to H-segments, H-sections group processes, that may belong to the same busy period. An H-section  $H_{ij}(\tau_{ab})$  is defined as follows:

$$H_{ij}(\tau_{ab}) = \{ \tau_{ij} \in hp_i(\tau_{ab}) \mid (\neg \exists \tau_{il} \in \Gamma_{ij} \Delta \Gamma_{ik} \mid \tau_{il} \in lp_i(\tau_{ab})) \}$$

(3.9)

The equation is similar to equation (3.8), with the difference that two processes in the same section must be preceded by the same process from  $lp_i(\tau_{ab})$ . This implies, that the processes in an H-section can be interconnected by some intermediate processes, that run on other reprocessing elements. In the following, we will always assume that the priority of segments and sections are given by  $\tau_{ab}$ . Therefore we will use the shorter notations,  $H_{ij}^{seg}$  and  $H_{ij}$ , where  $\tau_{ab}$  is implied.

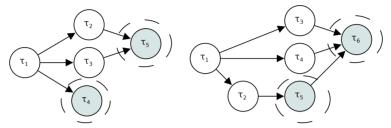

Figure 3.4: Examples of Segments and Sections

The example shown in Figure 3.4 will explain how H-sections and H-segments may look. Processes in Figure 3.4 are painted with fill color according to their priorities. The dark nodes on the graph mark the processes that are in  $hp_i(\tau_{ab})$ , the white nodes are processes in  $lp_i(\tau_{ab})$ , and the dashed node  $\tau_4$  represents a process, which runs on other processing element than  $\tau_{ab}$ . Using the definitions, we find four segments and three sections. The segments are  $H_{i2}^{seg} = H_{i5}^{seg} = H_{i5}^{seg}$

$\{\tau_2, \tau_5\}, \, H_{i3}^{seg} = \{\tau_3\}, \, H_{i7}^{seg} = \{\tau_7\}, \, H_{i8}^{seg} = H_{i9}^{seg} = \{\tau_8, \tau_9\}.$  The sections shown on in the figure are  $H_{i2} = H_{i4} = H_{i5} = H_{i7} = \{\tau_2, \tau_5, \tau_7\}, \, H_{i3} = \{\tau_3\}$  and  $H_{i8} = H_{i9} = \{\tau_8, \tau_9\}.$

An H-segment is preceded by a process,  $\tau_{ip} < H^{seg}_{ij}$ , when  $\tau_{ab}$  precedes all processes in the segment. In the example above process  $\tau_1$  precedes all segments in  $\Gamma_i$ ,  $\tau_6 < H^{seg}_8$  and  $\tau_4 < H^{seg}_7$ . A process is said to be an immediate predecessor of a segment, if one of its immediate successors belong to the segment. Processes, with an immediate predecessor in the segment, are called successors of the segment. The precedence properties are mostly important for H-segments, but they are defined in similar way for H-sections as well.

The analysis will study the contribution from all possible segments to the busy period. Similarly to the process phasing, it defines phasing relations between H-segments and the busy period, which are very close to equations (3.5) - (3.7). The phasing of an H-segment is determined by its offset and jitter, which are equal to the first process in the segment. The time from the start of the busy period to the arrival of the segment is given by:

$$\varphi_{ijk}^{seg}(\tau_{ab}) = T_i - \Phi_{ij}^{seg}(\tau_{ab}) - (\Phi_{ij} + J_{ij}) \mod T_i$$

(3.10)

and the number of the first pending instance of the segment at  $t_c$  is:

$$p_{0,ijk}^{seg}(\tau_{ab}) = 1 - \left[ \frac{J_{ij}^{seg}(\tau_{ab}) - \varphi_{ijk}^{seg}(\tau_{ab})}{T_i} \right]$$

(3.11)

The analysis can be further refined by the fact that some segments can block execution of other segments. Such segments are called *blocking segments*. Only one blocking segment among all blocking segments can execute within the busy period of  $\tau_{ab}$ . An H-segment is blocking when it has predecessors that belong to  $lp_i(\tau_{ab})$ . In Figure 3.4 (a) the blocking segments are  $H_{i2}^{seg}$ ,  $H_{i3}^{seg}$  and  $H_{i8}^{seg}$ . We return to the segments later, when we present our extensions. Now, the next step is to explain how the worst-case response time is computed by WCDOPS+.

## 3.1.4 Identifying the Contributions From Other Processes

By using phasing it is possible to find all combinations of processes and segments, that may contribute to  $\tau_{ab}$  busy period. The contribution is found from each transaction, including the one, process  $\tau_{ab}$  belongs to. For each transaction two kinds of contribution are computed - non-blocking interference  $W_i$ , and blocking interference  $W_i$ . The non-blocking interference is the maximum contribution from transaction  $\Gamma_i$ , when no blocking segments are allowed to execute within

the busy period, and the blocking interference is the maximum contribution from  $\Gamma_i$  when one blocking segment is allowed to execute within the busy period. The difference between blocking and non-blocking interference is called *interference increase*  $\Delta W_i = WB_i - W_i$ , and the interference increase is maximised among all transactions.

The transaction interference is found by using the function called *Transaction-Interference*, that locates the contribution from process instances arriving prior to  $t_c$  ( $p \le 0$ ). It considers all jobs of a transaction  $\Gamma_i$  that can possible interfere with  $\tau_{ab}$  in order to locate the worst interference. For each job, it uses the function BranchInterference to locate the longest<sup>1</sup> possible chain of higher priority processes that might contribute to the busy period. As not all processes of a given chain are able to actually contribute to the busy period, TaskInterference will eliminate these processes during the analysis. This is done by using so-called TaskInterference, which are simple conditions applied in TaskInterference. We refer to [34] and [35], where these rules are explained and formalised and the pseudocode is given. A more detailed description of TaskInterference will be given in Section 3.2.3, where we present our modifications to the algorithm.

As mentioned before, TransactionInterference finds two values for transaction contribution to the busy period, the blocking and non-blocking interference. However, we also need to find the contribution from instances, that might arrive after  $t_c$  (p>0). Due to precedence order, only instances of those processes that belong to the first H-section in the transaction can contribute to  $\tau_{ab}$  busy period. This requires that the first H-segment is not blocking. Those processes are found as follows:

$$MP_i(ab) = \{ \tau_{il} \in hp_i(\tau_{ab}) \mid (\neg \exists \tau_{ix} \in lp_i(\tau_{ab}) \mid \tau_{ix} < \tau_{il}) \}$$

$$(3.12)$$

The contributions from jobs arriving after  $t_c$  is then

$$W_{ik}(\tau_{ab}, w) \mid_{p>0} = \sum_{\tau_{ii} \in MP_i(ab)} \left[ \frac{w - \varphi_{ijk}^{seg}(\tau_{ab})}{T_i} \right]$$

(3.13)

Finally, the total contribution from a transaction  $\Gamma_i$  to the busy period of  $\tau_{ab}$  when process  $\tau_{ik}$  is used to start the busy period is given by

$$[W_{ik}(\tau_{ab}, w), WB_{ik}(\tau_{ab}, w)] = TransactionInterference(\tau_{ab}, \tau_{ik}, w) + W_{ik}(\tau_{ab}, w)|_{p>0}$$

(3.14)

But since there can be many processes that can start the busy period, all of them must be considered in order to find the upper bound on the blocking and

<sup>&</sup>lt;sup>1</sup>In terms of execution time

non-blocking interference and the largest interference increase:

$$W_i^*(\tau_{ab}, w) = \max_{\forall \tau_{ab} \in XP_i(\tau_{ab})} W_{ik}(\tau_{ab}, w)$$

(3.15)

$$W_i^*(\tau_{ab}, w) = \max_{\forall \tau_{ab} \in XP_i(\tau_{ab})} W_{ik}(\tau_{ab}, w)$$

$$WB_i^*(\tau_{ab}, w) = \max_{\forall \tau_{ab} \in XP_i(\tau_{ab})} WB_{ik}(\tau_{ab}, w)$$

$$(3.15)$$

$$\Delta W_i^*(\tau_{ab}, w) = W B_i^*(\tau_{ab}, w) - W_i^*(\tau_{ab}, w)$$

(3.17)

The set  $XP_i$  used in (3.15) and (3.16) contains all processes in the transaction  $\Gamma_i$ , that come first in their H-segments. The contribution from the transaction  $\Gamma_a$ , which process  $\tau_{ab}$  belongs to, is found separately, but in a similar way.

#### 3.1.5 Deriving the Response Times

It is now possible to explain how the worst case response time of process  $\tau_{ab}$ is computed. The analysis is done for all instances of process  $\tau_{ab}$ . For a single instance the *completion time* consists of following parts: the maximum blocking from low priority processes  $B_{ab}$ , (ignored in this thesis), the non-blocking interference from transaction  $\Gamma_a$ , the sum of non-blocking interferences from all other transactions and the maximum blocking interference increase  $\Delta W_{ac}^*$ , due to one blocking H-segment among all transactions. The completion time of  $p_{ab}$ is given by this equation:

$$w_{abc}(p_{ab}) = B_{ab} + W_{ac}(\tau_{ab}, w, p_{ab}) + \sum_{\forall i \neq a} W_i^*(\tau_{ab}, w, \tau_{ac}) + \Delta W_{ac}^*(\tau_{ab}, w, \tau_{ac})$$

(3.18)

The response time of instance  $p_{ab}$  is found by subtracting the arrival time of the instance from the completion time,  $w_{abc}$ , and adding the offset,  $\Phi_{ab}$ . The subtraction will reduce the completion time to the amount that overlaps with the busy period:

$$R_{abc}^{w}(p_{ab}) = (w_{abc}(p_{ab}) - (\varphi_{abc} + (p_{ab} - 1)T_a)) + \Phi_{ab}$$

(3.19)

Notice that the first part of the equation without adding the offset is called local response time. The global response times include offsets, and they are computed when local response times have been found for all processes. The number of instances of  $\tau_{ab}$  can be found, when we know the maximum length of the busy period of  $\tau_{ab}$ , as previously shown in Figure 3.3. The upper bound

for the length of the busy period of  $\tau_{ab}$ ,  $L_{abc}$ , is computed as follows:

$$L_{abc} = B_{ab} + W_{ac}' + \sum_{\forall i \neq a} W_i^*(\tau_{ab}, L, \tau_{ac}) + \max(W B_{ac}' - W_{ac}', \Delta W_i^*(\tau_{ab}, L, \tau_{ac}))$$

(3.20)

The length of the busy period is used to find the latest instance of the H-segment  $H_{ac}^{seg}(\tau_{ab})$

$$p_{L,abc}^{seg}(\tau_{ab}) = \left[\frac{L_{abc} - \varphi_{0,abc}^{seg}(\tau_{ab})}{T_a}\right]_0 \tag{3.21}$$

so the possible instance numbers of  $\tau_{ab}$  are included in the interval from  $p_{0,abc}^{seg}(\tau_{ab})$  to  $p_{L,abc}^{seg}(\tau_{ab})$ . The final worst-case response time of process  $\tau_{ab}$  is the response time of the instance having the largest response time, maximised over all possible combinations with processes that may start the busy period:

$$R_{ab}^{w} = \max_{\forall \tau_{ac} \in XP_{a}(\tau_{ab})} \left[ \max_{p_{ab} = p_{0,abc}^{seg}(\tau_{ab}) \dots p_{L,abc}^{seg}(\tau_{ab})} R_{abc}^{w}(p_{ab}) \right]$$

(3.22)

The equations above are solved by using fixed-point iteration, and by applying equation (3.22) to all processes in the system, the local response times are found. When response times have been found for all processes, the algorithm updates the offsets and jitters by using formulas (3.1) and (3.2). A simple pseudocode illustrating the outer loop of the algorithm is shown below:

#### Algorithm 1 Outer Loop of WCDOPS+

```

\label{eq:constraints} \begin{split} & \operatorname{initLocalResponseTimes}(\mathcal{A}) \\ & \operatorname{repeat} \\ & \text{for all } \Gamma_i \in \mathcal{A} \text{ do} \\ & \text{ for all } \tau_{ab} \in \Gamma_i \text{ do} \\ & \text{ findLocalResponseTimes}(\tau_{ab}) \text{ } \{ \operatorname{Equation} \text{ } (3.22) \} \\ & \text{ end for} \\ & \text{ end for} \\ & \text{ for all } \Gamma_i \in \mathcal{A} \text{ do} \\ & \text{ updateGlobalResponseTimes}(\Gamma_i) \\ & \text{ updateJitterAndOffset}(\Gamma_i) \text{ } \{ \operatorname{Equations} \text{ } (3.1) \text{ } - \text{ } (3.2) \} \\ & \text{ end for} \\ & \text{ until converged} \end{split}

```

When WCDOPS+ detects that there are no changes in the response times, it stops, and the analysis is said to have converged.

#### 3.1.6 Messages and Non-Preemptive Processes

The analysis also includes support for non-preemptive scheduling. It allows us to do response time analysis of the communication on a CAN bus by treating messages as non-preemtive processes. Each communication channel will be represented as a pseudo processing element. Consequently, equation (3.18) is used to find the queuing time of a message  $m_{ab}$ . The queuing time corresponds to the completeion time of a process, except that it does not include the transmission time of the message itself. As the message cannot be preempted during the transmission, queuing implies the time that it needs to wait before starting the transmission. Therefore the idea is to find the worst case queuing time due to other messages having equal or higher priorities.

The analysis is extended by adding extra conditions to the reduction rules Task-Interference and modifying the contribution coming from instances arriving when p>0. Another adjustment is done by introducing the maximum blocking time from lower priority messages, which is bounded by the maximum transmission time of all lower priority messages allocated to the same communication channel as  $m_{ab}$

$$B_{ab} = \max_{\forall i, \forall m_{ij} \in lp_i(\tau_{ab})} C_{ij}^m \tag{3.23}$$

This maximum blocking time is used when finding the worst case queuing time,  $q_{abc}(m_{ab})$ , which is similar to equation (3.18), where the blocking time was ignored. In the rest of the algorithm the messages are handled as they were processes. We apply this approach directly as defined by Redell.

## 3.2 Allowing Several Predecessors

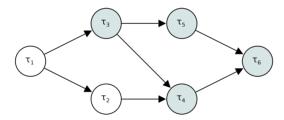

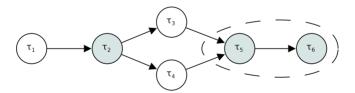

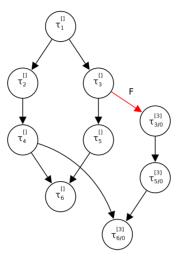

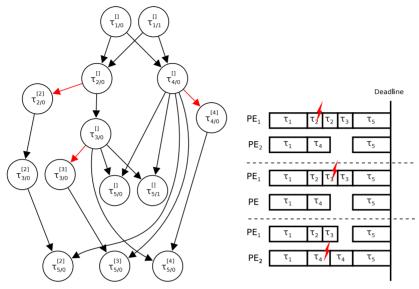

The original analysis only supports one predecessor for each process, and in our case it will cause problems when using replication as fault tolerance technique. The reason being that when a process is replicated, its successors will have several predecessors. An example can be seen in Figure 3.5, where  $\tau_2$  and  $\tau_3$  will each get two predecessors when replication is added to all processes.

(a) The original process graph.

(b) The corresponding fault-tolerant process graph where all processes are protected with replication and  $\kappa=1$ .

Figure 3.5: Example illustrating that replication will create several predecessors to processes,  $\tau_2$  and  $\tau_3$

Instead of focusing on the consequences of replication, we consider the problem more generally. We will therefore modify the algorithm, such that several predecessors are allowed, and thereby also including the special case of replication. In each of the following subsections we will start by describing the modifications strictly necessary to allow several predecessors, and then try to reduce any pessimism introduced by the modifications.

We use  $pred(\tau_{ab})$  to denote the set of immediate predecessors to process  $\tau_{ab}$ , and  $succ(\tau_{ab})$  as immediate successors to  $\tau_{ab}$ . Starting from the very beginning, we need to consider how jitters and offsets need to be updated, when a process is preceded by several processes.

#### 3.2.1 Offsets and Jitters

The offset represents the minimum delay for the arrival of process  $\tau_{ab}$  due to the execution of preceding processes. It is given by the best case response time of the preceding process  $\tau_{ap}$ , which implies that process  $\tau_{ab}$  cannot start before its predecessor  $\tau_{ap}$  has been executed.

When we have several predecessors, we can no longer compute the offset as defined in equation (3.1). However, we still want the offset to express the earliest possible arrival of  $\tau_{ab}$ . And the offset then becomes the latest possible best case

response time among all predecessors of process  $\tau_{ab}$

$$\Phi_{ab}^{1} = \max_{\forall \tau_{ap} \in pred(\tau_{ab})} R_{ap}^{b} \tag{3.24}$$

This way of updating the offsets is very simple, and it works correctly when the predecessors run on different processing elements or when there is only one predecessor. However, if some of the predecessors are mapped on the same processing element, the value of the offset might be less correct. The reason being that the best case response time is found by adding the offset and the best case execution time  $C^b$  only. If some of the predecessors run on the same processing elements, the best case response times of the predecessors will be too optimistic (too low) since they will preempt each other and may force the analysis to consider some phasings that are not possible.

Nevertheless, this problem will not lead to incorrect worst case reponse times, because the preemption will be contained by jitters, as they depend on the worst case response time,  $R^w$ , that includes the interference from other processes. And since the phasing of processes and segments does depend on jitters, the computation of release times is still valid.

We can improve equation (3.24) and thereby fine tune the values of the offsets. It is possible, because we know that predecessors of  $\tau_{ab}$  running on the same processing element may preempt each other. Therefore we propose a modification to the algorithm that can find more exact values of the offsets in order to speed up the convergence of the algorithm.

We start by grouping  $\tau_{ab}$  predecessors into sets by their respective processing elements, as shown by equation (3.25) below

$$SPE(N_i, \tau_{ab}) = \{ \tau_{ap} \in pred(\tau_{ab}) \mid \mathcal{M}(\tau_{ap}) = N_i \}$$

(3.25)

Each group is then considered to produce a total best case delay equal to the sum of all best cases execution times  $C^b$ , and an initial offset, equal to the least offset among all processes in the group. The sum of the initial offset and the total best case delay is treated as possible offset candidate, and the largest offset candidate is selected as the offset to process  $\tau_{ab}$

$$\Phi_{ab}^{2} = \max_{\forall N_i \in \mathcal{N}} \left[ \min_{\forall \tau_{ap} \in SPE(N_i, \tau_{ab})} (\Phi_{ap}) + \sum_{\forall \tau_{ap} \in SPE(N_i, \tau_{ab})} (C_{ap}^b) \right]$$

(3.26)

The offset found in equation (3.26) will be larger than (3.24) in some situations, but not all. To ensure that the offset is always on the safe side, we take the maximum of these two equations, such that the final version of the offset becomes

$$\Phi_{ab} = \max(\Phi_{ab}^{1}, \Phi_{ab}^{2}) \tag{3.27}$$

The jitters are found in a similar way to offsets. A jitter is used to express the maximum delay, a process  $\tau_{ab}$  can expire after it has arrived at time  $\Phi_{ab}$ . This maximum delay is therefore found as the difference between the earliest possible arrival of the process  $\tau_{ab}$  and the latest time for release, i.e. when all predecessors are completed. If we look at the predecessors, we can notice, that the worst case response time of each predecessor contains interference from other processes, including other predecessors of  $\tau_{ab}$ . Hence the predecessor having largest response time can be used to find the jitter of process  $\tau_{ab}$  as follows:

$$J_{ab} = \max_{\forall \tau_{ap} \in pred(\tau_{ab})} R_{ap}^{w} - \max_{\forall \tau_{ap} \in pred(\tau_{ab})} R_{ap}^{b}$$

(3.28)

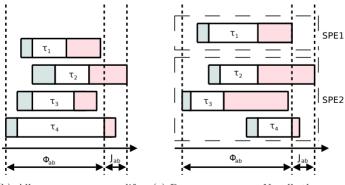

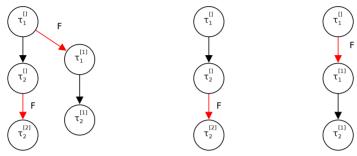

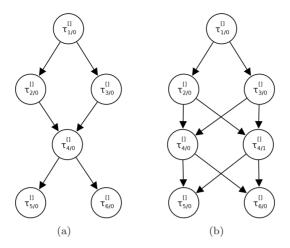

It is shown in Figure 3.6 how the offset and the jitter are found for  $\tau_{ab}$ . The predecessors of  $\tau_{ab}$  are  $pred(\tau_{ab}) = \{\tau_1, \tau_2, \tau_3, \tau_4\}$ . The white boxes represent the best case response time, the light-blue boxes are offsets, and the pink boxes add the part from the worst case response time.

(a) A process graph, where process  $\tau_{ab}$  has four predecessors.

(b) All processes run on different processing elements.

(c) Process  $\tau_1$  runs on  $N_1$ , all other processes run on  $N_2$ .

Figure 3.6: Illustrating the calculation of jitter and offset of process  $\tau_{ab}$ .

In the first case, Figure 3.6(b), all predecessors are mapped to different processing elements, and the offset is found according to equation (3.24), i.e. the maximum best case response time among all predecessors, which is  $\tau_4$  in the example above. In Figure 3.6(c) processes  $\tau_2$ ,  $\tau_3$  and  $\tau_4$  run on the same processing element, and the offset is computed as the sum of their best case execution times plus the minimal offset among them.

After each iteration of the algorithm all local response times are re-computed. The jitters, the offsets and the global response times are updated for each process based on the newly found numbers. The offsets and the jitters of process  $\tau_{ab}$  are computed with values retrieved from its predecessors. When considering just a single predecessor, updating of the processes is done recursively in depth-first way. In the cases with several predecessors, the changes must be propagated in a breadth-first way, because all predecessors of  $\tau_{ab}$  must be updated before updating process  $\tau_{ab}$  itself.

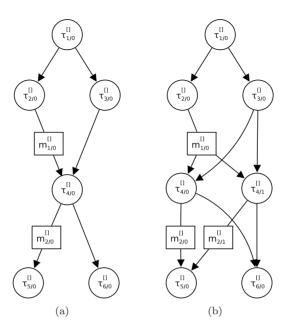

#### 3.2.2 H-sections and H-segments

The next part of our modifications concerns changes in the definitions of H-segments and H-sections. Recall, that all processes of a segment will belong to the busy period of the process under analysis. In order to satisfy this property with several predecessors, we must derive a new definition of H-segments and H-sections.

The original requirement that all processes in a segment must be in  $hp_i(\tau_{ab})$  is unchanged, but we need to redefine the condition whether two process from  $hp_i(\tau_{ab})$  are in the same segment. Two processes having higher priority than  $\tau_{ab}$  belong to the same segment, only if they have the same set of nearest ancestors that are not in  $hp_i(\tau_{ab})$ . When working on segments, this set of ancestors of process  $\tau_{ik}$  is formally defined as:

$$SP^{seg}(\tau_{ab}, \tau_{ik}) = \{ \tau_{if} \in \Gamma_i \mid \notin hp_i(\tau_{ab}) \land \tau_{if} < \tau_{ik} \land (\neg \exists \tau_{il} \notin hp_i(\tau_{ab}) \mid \tau_{if} < \tau_{il} \land \tau_{il} < \tau_{ik}) \}$$

(3.29)

This requirement is also used for building H-sections, and two processes from  $hp_i(\tau_{ab})$  are in the same H-section if they have identical ancestor sets, which are defined below:

$$SP(\tau_{ab}, \tau_{ik}) = \{ \tau_{if} \in lp_i(\tau_{ab}) \mid (\tau_{if} < \tau_{ik} \land (\neg \exists \tau_{il} \in lp_i(\tau_{ab}) \mid \tau_{if} < \tau_{il} \land \tau_{il} < \tau_{ik})) \}$$

(3.30)

All hp-processes in Figure 3.7 have different SP-sets, as they have different ancestors  $SP^{seg}(\tau_{ab}, \tau_4) = \{\tau_2\}$ ,  $SP^{seg}(\tau_{ab}, \tau_5) = \{\tau_3\}$   $SP^{seg}(\tau_{ab}, \tau_6) = \{\tau_2, \tau_3\}$ .

Figure 3.7: Since  $\tau_4$ ,  $\tau_5$  and  $\tau_6$  each have different SP sets, they are in different segments

Now, we can derive the updated definitions of H-segments

$$H_{ij}^{seg}(\tau_{ab}) = \{ \tau_{ik} \in hp_i(\tau_{ab}) \mid SP^{seg}(\tau_{ab}, \tau_{ij}) = SP^{seg}(\tau_{ab}, \tau_{ik}) \}$$

(3.31)

and H-sections

$$H_{ij}(\tau_{ab}) = \{ \tau_{ik} \in hp_i(\tau_{ab}) \mid SP(\tau_{ab}, \tau_{ij}) = SP(\tau_{ab}, \tau_{ik}) \}$$

(3.32)

The new definitions for H-sections and H-segments are backward compatible with the original ones, given by equations (3.9) and (3.8). The reason is because intermediate processes in  $lp(\tau_{ab})$  are still not allowed. A process is said to precede an H-segment if it precedes all processes in the segment,  $\tau_{ab} < H_{ij}^{seg}(\tau_{ab})$ . As each process can have more than one predecessor, the set of immediate predecessors to an H-segment  $pred(H_{ab}^{seg}(\tau_{ij}))$  has to be updated to reflect this:

$$pred(H_{ij}^{seg}(\tau_{ab})) = \{\tau_{ip} \in \Gamma_i | \tau_{ip} < H_{ij}^{seg}(\tau_{ab}) \land (\exists \tau_{ik} \in H_{ij}^{seg}(\tau_{ab}) | \tau_{ip} \in pred(\tau_{ik}))\}$$

(3.33)