### CHAPTER

# Introduction

# 1.1 Abstract

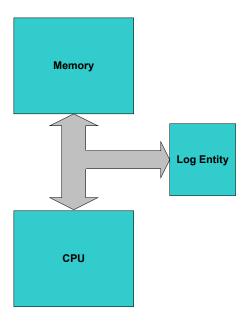

In this thesis, we have designed a core model of microprocessor that can be used for performance evaluation of any communication architecture. In its outer form, this model is an entity in VHDL. To do performance evaluation for any communication architecture, several instances of this entity can be made depending upon the requirement and are then connected to the memory according to the configuration of that communication architecture. These models then generate traffic on the bus to communicate with the memory. At the end, these models generate report about their performance. Most important in that report is the effective CPI (Cycles per Instruction) under the given communication architecture.

The main feature of this model is that it performs simulation very fast as compared to the behavior models of microprocessors. For e.g., it can simulate 1 million instructions in nearly 1-2 minutes on SUN machines. Whereas, the complex models of microprocessors require 2-3 hours or even more for the same number of instructions. Moreover, it doesn't require any software to run i.e. to perform simulation it does not require that some software should be loaded into the memory. It can perform simulation without any original software to generate some performance statistics.

Although in its outer form it is a core model of a microprocessor (an entity in VHDL), it can also be termed as a 'tool' to analyze performance of a system. Because it can only be used for performance estimation purposes and is not a hardware design.

# 1.2 Background

Systems on chips (SOC) are becoming increasingly more complex and dense. A single SOC design may consist of a processor, memory, some dedicated hardware and Input/output interface. SOC designs that consist of more than 1 processor are common these days. To deal with the complexity, we rely on use of intellectual Property (IP) cores. With increasing number of IP cores, it is important to connect these in a structured and efficient way. The communication architecture becomes essential in providing a flexible platform, and it is essential for the overall SOC performance. Decisions about the communication architecture should be made as early as possible in the design process.

These decisions have been made by simulating the system and evaluating the performance of the system. By performance, we mean how fast the system completes its task. However simulating the system with the real cores is too slow and time consuming. It is not possible to simulate a system in a short period of time that consists of many complex IP cores. At the early phase of the design, which is likely to undergo lot of changes it is not a good idea to spend too much time on extensive simulation. A general rough estimation is quite enough at the start of the design. Therefore methods for faster performance simulation are always attractive and a tradeoff between faster execution and accurate performance estimation is justified. Hence at the early phase of design process, we can replace the real cores with their simple core models. These core models are much faster to simulate than the real cores.

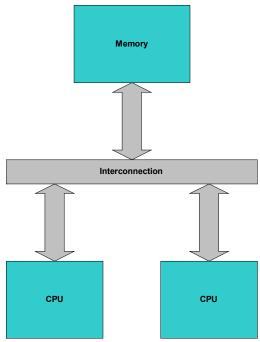

When dealing with performance evaluation we are not interested in the functionality of the system. For example, if we have to make a performance estimation of a system comprising of two processors sharing a single memory, we are only interested in knowing how frequently the processors communicate with the memory, how many times we have a conflict between processors to access the memory, how much time the processor remains stalled waiting for its turn to access the memory, is the memory has been efficiently shared or not etc.

Figure 1.1 Two CPUs sharing the interconnection network to access the single memory

For simulation we also need software that is going to be executed on the processor. The processor communicates with the memory architectures when it needs instructions which are not in its cache or when it requires some data which are not in its cache as well. This behavior largely depends on the software and different softwares generate different traffic. It can be a case that we don't know which software would be executed on this given architecture. It is also difficult to get a significant number of softwares that are written for performance estimation.

Hence the objective is that we don't know which software is going to be executed on a given architecture and so we don't want to make performance estimation by running few self-made programs

In this project, we have targeted on these two different problems:

- If we don't know what software would be executed on a given architecture then how can we make the performance estimation?

- How can we make the simulation much faster than the simulation that involves real cores or the behavior models of the cores?

To tackle the first problem, we will make some models of the different program behaviors and a core model of microprocessor uses these behaviors to generate traffic that involves communication with the outside environment. Since we are not executing any real program, the job of the core model is to generate traffic only. This means that the model would not do any thing for the instructions, which do not involve communication with the memory. The communication with the memory takes place when the processor needs instruction to execute which is not found in the instruction cache or when the

processor needs to read or write some data, which is not in the data cache. The former case would happen only when the instruction is not found in the instruction cache and the latter case would happen only when the given instruction is either load or store and the processor faces a data miss in the data cache. Thus whenever there is a miss in either instruction or data cache the processor communicates with the memory and there is traffic on the bus connecting the processor and the memory. The job of the model is to make decisions at which time traffic is generated i.e. when there is a miss in the cache. As there is no real software executing on the model so it has to make this decision by its own. This requires some input parameters from the user of this model. Some of these parameters are:

- Number of instructions

- Load/store instructions

- Cycles per instruction (CPI)

- Instruction miss rate

- Data miss rate

Based on these parameters the microprocessor model would communicate with the memory from time to time. Our job is to study different program behaviors that cause communication between the CPU and the memory and characterize these behaviors in the CPU model. Thus the CPU model will generate traffic that looks like a normal program executing on the processor.

In most CAD tools, which are used for performance evaluation, we provide them some software to execute along with some cache configuration parameters (cache size, block size etc.). These tools then calculate the effective instruction and data miss rate. Our model, nearly works in opposite direction. It takes total number of instructions, instruction miss rate and data miss rate as an input and then generate different possible sequences of these misses. In other words, by using these inputs it generates different possible traffic patterns that may result due to different types of softwares.

Hence we will develop a CPU model, which can generate traffic by using some input parameters that statically corresponds to the real cores and also do some performance measurements like execution time of given number of instructions, no of memory accesses, effective CPI, number of clock cycles CPU remains stalled waiting for the memory, number of clock cycles during which CPU is perfectly in execution etc. We can connect this CPU model in different configurations and then evaluate the traffic statistics between different components. In a multiprocessing environment the performance is highly dependent on the communication architecture and different configurations may result in different performance results.

The second requirement is to make it much faster than normal simulation. This simulation should be very fast because in the absence of real software the performance estimation would not be very accurate. The aim is to get some rough approximation at the very early stage of design process.

In fact, the steps taken to solve the first requirement have also solved the second requirement. When simulating with real cores the simulation of every instruction consumes some time. The simulator needs to record every event that happened inside or outside the CPU. However in our model we only do some processing in the case of a miss. So in every clock cycle we just need to make decision whether we have a miss or not. The simulation time for making such decisions is much smaller than the time for simulating real processor core that involve lot of signals and millions of gates. Off course the high-level behavior models of the processors can do the performance simulation. But still it doesn't provide that much speedup and also they require software to be executed on these models.

Therefore the simulation with this behavior model of a microprocessor would be much faster than executing any program on the processor as well as it doesn't contain any effect introduce by a particular program. As mentioned earlier, since we are only interested in the performance it is possible to make some rough estimate of the system without executing the software.

The CPU model is designed to be used in different architectures; therefore it is necessary that it should follow some standard interface. The CPU model follows the Open Core Protocol (OCP) interface i.e. it can be connected to any component that follows the OCP interface. Or we can say that the communication between the processor and the memory would be through some interconnect following the OCP. The relevant details of OCP are given in Chapter 2.

Developing CPU model requires a lot of programming features, which are hard to find in a Hardware Description Language like VHDL. Therefore the model is written in C language. However most of the IP cores currently used in the industry are in VHDL. As a result of this, we need to work in a mixed language environment with our processor model in C language and the other cores which are connected with the model are in VHDL. This requires an interface between C and VHDL. So that when seen from outside, the model looks like an entity written in VHDL but from inside, its all functionality is written in C language. We have used Foreign Language Interface (FLI) provided by the tool ModelSim. This means that our simulation environment consists of our model written in C language and the other cores written in VHDL all running in ModelSim. It may happen that in a given test bench we have more than one copies of our model along with other IP cores (written in VHDL) all connected to each other through OCP. The relevant details of FLI and its use in the thesis are given in Chapter 3.

# 1.3 Tasks of the project

Based on the above discussion we can say that we need to develop a core model of the general-purpose microprocessor that must have the following characteristics:

- It must follow the OCP and FLI interface.

- It must be able to generate traffic according to the input parameters discussed above.

- The simulation with the model should be much faster than the simulation with the real core.

- The statistics generated by the model should be reasonably accurate when compared with real program execution.

The next two chapters give an overview of OCP and FLI and the features, which are used in the model. Chapters 4 and 5 include the discussion how the misses have been introduced or we can say how the traffic has been generated. Chapter 6 deals with the discussion related to the testing of the model.

# 1.4 SUMMARY

In this chapter, we have introduced our project. We have described the motivation behind this project and our proposed steps that we will take to complete the requirements of the project. At the end, we have set the tasks that have to be met in this project.

We will design a CPU model, which is following OCP interface. The purpose of the model is to do faster simulation to make some performance measurements. It has to do these performance calculations without using any software. In the absence of real software, the task of the model is to behave in a manner as some real software is executing on it. This model is supposed to be used at the very early phase of design process where the tradeoff between accuracy and speed can be justified to a larger extent.

## CHAPTER

# 2

# Open Core Protocol

When an instruction or data miss occurs in a CPU, the CPU needs to communicate with the memory. This communication is brought through some protocol, which defines how the request to read or write data will be generated, how the memory responds to the request, how many minimum clock cycles are required to complete the data transfer, etc. The interface of the CPU and the memory (or any component which needs to communicate with the outside world) is designed according to that protocol. It means that any two or more components that follow the same protocol can be connected to each other without any modifications in the design.

We have used Open Core Protocol (OCP) in our CPU model. Since our CPU model can be used only for simulation there is no particular advantage of using any kind of protocol. We have used OCP because it is the most fast emerging protocol. To make simulation in any environment the CPU model needs to be connected with some other entities. Since OCP is the most widely used protocol these days, so it is very likely that the simulation would be done in an environment where the entities are following the OCP protocol.

The OCP defines complete standard from the basic data flow signals to the signals that are used for test purposes. Broadly, OCP signals can be divided into two main categories, the basic OCP signals and the optional OCP signals. The presence of basic OCP signals in any core is necessary if it is following the OCP interface. The optional OCP signals can be included according to the requirement. In our model, we have used only the basic OCP signals and very few optional signals. These signals are included both in our CPU model and the memory, which we have designed for testing purposes.

This chapter covers the very basic introduction about the OCP. Only the features used in the thesis are described here. Detailed information can be found from the online manual of OCP at <a href="www.ocp-ip.com">www.ocp-ip.com</a>.

# 2.1 An Overview of Open Core Protocol

The Open Core Protocol (OCP) defines a high-performance, bus-independent interface between IP cores that reduces design time, design risk, and manufacturing costs for SOC designs.

An IP core can be a simple peripheral core, a high-performance microprocessor, or an onchip communication subsystem such as a wrapped on-chip bus. The Open Core Protocol:

- Achieves the goal of IP design reuse. The OCP transforms IP cores making them independent of the architecture and design of the systems in which they are used.

- Optimizes die area by configuring into the OCP only those features needed by the communicating cores.

- Simplifies system verification and testing by providing a firm boundary around each IP core that can be observed, controlled, and validated.

# 2.1.1 OCP Characteristics

The OCP defines a point-to-point interface between two communicating entities, such as IP cores and bus interface modules (bus wrappers). One entity acts as the master of the OCP instance, and the other as the slave. Only the master can present commands and is the controlling entity. The slave responds to commands presented to it, either by accepting data from the master, or presenting data to the master. For two entities to communicate in a peer-to-peer fashion, there need to be two instances of the OCP connecting them - one where the first entity is a master, and one where the first entity is a slave. *In our case, the CPU is the master and the memory is a slave entity*.

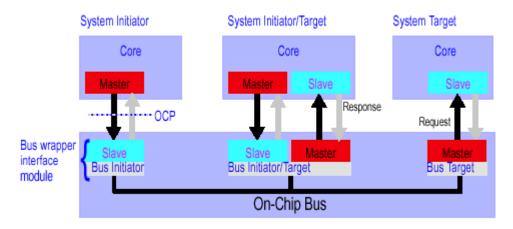

Figure 2.1 shows a simple system containing a wrapped bus and three IP core entities: one that is a system target, one that is a system initiator, and an entity that is both.

The characteristics of the IP core determine whether the core needs master, slave, or both sides of the OCP; the wrapper interface modules must act as the complementary side of the OCP for each connected entity. A transfer across this system occurs as follows. A system initiator (as the OCP master) presents command, control, and possibly data to its connected slave (a bus wrapper interface module). The interface module plays the request across the on-chip bus system. The OCP does not specify the embedded bus functionality. Instead, the interface designer converts the OCP request into an embedded bus transfer. The receiving bus wrapper interface module (as the OCP master) converts the embedded bus operation into a legal OCP command. The system target (OCP slave) receives the command and takes the requested action. Each instance of the OCP is configured (by choosing signals or bit widths of a particular signal) based on the requirements of the connected entities and is independent of the others.

Figure 2.1 System Showing Wrapped Bus and OCP instances

For instance, system initiators may require more address bits in their OCP instances than do the system targets; the extra address bits might be used by the embedded bus to select which bus target is addressed by the system initiator.

The OCP is flexible. There are several useful models for how existing IP cores communicate with one another. Some employ pipelining to improve bandwidth and latency characteristics. Others use multiple-cycle access models, where signals are held static for several clock cycles to simplify timing analysis and reduce implementation area. Support for this wide range of behavior is possible through the use of synchronous handshaking signals that allow both the master and slave to control when signals are allowed to change.

# 2.1.2 OCP Interface Signals

OCP interface signals are grouped into dataflow, sideband, and test signals. A small set of the signals from the dataflow group called the basic OCP, is required in all OCP configurations. Optional signals can be configured to support additional core communication requirements. The optional dataflow signals are divided into simple and complex extensions. All sideband and test signals are optional. We will restrict our discussion to only basic OCP signals and signal used in burst access, which is in simple OCP extension category.

The OCP is a synchronous interface with a single clock signal. All OCP signals are driven with respect to and sampled by the rising edge of the OCP clock. *Except for clock and reset, OCP signals are strictly point-to-point and uni-directional.*

#### **Dataflow Signals**

The dataflow signals consist of a small set of required signals called the basic OCP and optional signals that can be configured to support additional core communication requirements. The optional dataflow signals are grouped into simple and complex extensions.

The naming conventions for dataflow signals use the prefix M for signals driven by the OCP master and S for signals driven by the OCP slave.

#### **Basic Signals**

Table 2.1 lists the basic OCP signals that must be present in any OCP interface.

| Name       | Width          | Driver | Function               |

|------------|----------------|--------|------------------------|

| Clk        | 1              | Varies | OCP clock              |

| MAddr      | 1-32           | Master | Transfer address       |

| MCmd       | 3              | Master | Transfer command       |

| MData      | 8/16/32/64/128 | Master | Write data             |

| SCmdAccept | 1              | Slave  | Slave accepts transfer |

| SData      | 8/16/32/64/128 | Slave  | Read data              |

| SResp      | 2              | Slave  | Transfer response      |

**Table 2.1: Basic OCP Signals**

#### Clk

Clock signal for the OCP. All interface signals are synchronous to the rising edge of Clk.

#### **MAddr**

The Transfer address, MAddr specifies the slave-dependent address of the resource targeted by the current transfer.

#### **MCmd**

Transfer command. This signal indicates the type of transfer at the OCP. Commands are encoded as follows in table 2.2.

| MCmd[2:0] | Transaction Type | Mnemonic |

|-----------|------------------|----------|

| 000       | Idle             | IDLE     |

| 001       | Write            | WR       |

| 010       | Read             | RD       |

| 011       | ReadEx           | RDEX     |

| 100       | Reserved         |          |

| 101       | Reserved         |          |

| 110       | Reserved         |          |

| 111       | Broadcast        | BCST     |

**Table 2.2: Command Encoding**

#### **MData**

Write data. This field carries data from the master to the slave.

#### **SCmdAccept**

Slave accepts transfer. A value of 1 on the SCmdAccept signal indicates that the slave accepts the master's transfer request.

#### **SData**

Read data. This field carries data from the slave to the master.

#### SResp

Response field from the slave to a transfer request from the master. Response encoding is as follows in table 2.3.

| SResp[1:0] | Response           | Mnemonic |

|------------|--------------------|----------|

| 00         | No response        | NULL     |

| 01         | Data valid/ accept | DVA      |

| 10         | Reserved           |          |

| 11         | Response error     | ERR      |

**Table 2.3: Response Encoding**

#### **MBurst**

Burst type. This signal allows linking related transfers into a burst transaction. It is configured into the OCP using the burst parameter. Mburst is not a basic OCP signal. It encodes both the burst type and the burst code, as shown in the Table 2.4.

| MBurst[2:0] | Burst Type          | Burst Code |

|-------------|---------------------|------------|

| 000         | All                 | LAST       |

| 001         | Incrementing        | TWO        |

| 010         | Incrementing        | FOUR       |

| 011         | Incrementing        | EIGHT      |

| 100         | Custom (packed)     | DFLT1      |

| 101         | Custom (not packed) | DFLT2      |

| 110         | Streaming           | STRM       |

| 111         | Incrementing        | CONT       |

**Table 2.4: Burst Encoding**

All these interface signals are used in CPU (Master) and (Memory). The VHDL declarations of CPU and Memory are shown in fig 2.2 and 2.3. It should be noted that in OCP the width of the address and data signals could be varied according to the requirement. Therefore their widths are declared as 'generic'.

```

entity cpu is

generic (

addr width: integer;

data width: integer);

port (

nreset

: in bit;

clk

: in bit;

-- OCP signal

SCmdAccept

: in bit;

-- OCP signal

: in bit vector(1 downto 0);

-- OCP signal

SResp

: in bit vector(data width-1 downto 0);

-- OCP signal

SData

: out bit vector(2 downto 0);

-- OCP signal

MCmd

: out bit vector(2 downto 0);

-- OCP signal

MBurst

: out bit vector(addr width-1 downto 0);

-- OCP signal

MAddr

MData

: out bit vector(data width-1 downto 0);

-- OCP signal

cpu stall

: out bit;

cpu out

: out bit);

end cpu;

```

Figure 2.2 VHDL declaration of CPU model following the OCP interface

```

entity memory is

generic (

addr width: integer;

data width: integer);

port (

nreset

: in bit;

clk

: in bit;

-- OCP signal

: in bit vector(2 downto 0);

-- OCP signal

MCmd

: in bit vector(2 downto 0);

-- OCP signal

MBurst

: in bit vector(addr width-1 downto 0);

-- OCP signal

MAddr

: in bit vector(data width-1 downto 0);

-- OCP signal

Mdata

SCmdAccept

: out bit;

-- OCP signal

: out bit vector(1 downto 0);

-- OCP signal

SResp

SData

: out bit vector(data width-1 downto 0)

-- OCP signal

);

end memory;

```

Figure 2.3 VHDL declaration of Memory model following the OCP interface

# 2.1.3 Timing Diagrams

The following timing diagrams show the data transfer in its various forms between the Master and the Slave using OCP basic signals. The data transfer would become more versatile by the addition of simple and complex extensions. In our case, consider the Master as a CPU, which is originating communication with the memory, which is acting as a slave.

## Simple Write and Read Transfer

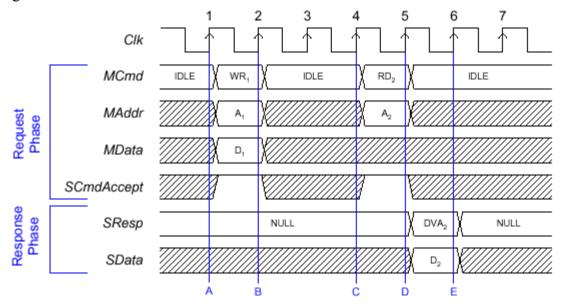

Figure 2.4 illustrates a simple write and read transfer on a basic OCP interface. This diagram shows typical behavior for a synchronous SRAM or for the control and status registers of a core.

Figure 2.4 Simple Write and Read Transfer

#### Sequence

A. The master starts a request phase on clock 1 by switching the MCmd field from IDLE to WR. At the same time, it presents a valid address  $(A_1)$  on Addr and valid data  $(D_1)$  on MData. The slave asserts SCmdAccept in the same cycle, making this a 0-latency transfer.

- B. The slave captures the values from MAddr and MData and uses them internally to perform the write. Since SCmdAccept is asserted, the request phase ends.

- C. The master starts a read request by driving RD on MCmd. At the same time, it presents a valid address on MAddr. The slave asserts SCmdAccept in the same cycle for a request-accept latency of 0.

- D. The slave captures the value from MAddr and uses it internally to determine what data to present. The slave starts the response phase by switching SResp from NULL to DVA.

The slave also drives the selected data on SData. Since SCmdAccept is asserted, the request phase ends.

E. The master recognizes that SResp indicates data valid and captures the read data from SData, completing the response phase. This transfer has request-to-response latency of 1.

#### Request Handshake

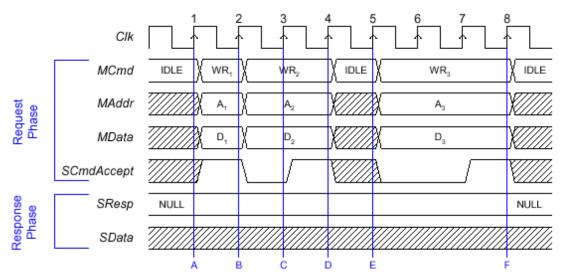

Figure 2.5 illustrates the basic flow-control mechanism for the request phase using SCmdAccept. There are three write transfers, each with a different request accept latency.

Figure 2.5 Request Handshake

#### Sequence

A. The master starts a write request by driving WR on MCmd and valid address and data on MAddr and MData, respectively. The slave asserts SCmdAccept in the same cycle, for a request accept latency of 0.

- B. The master starts a new transfer in the next cycle. The slave captures the write address and data. It deasserts SCmdAccept, indicating that it is not yet ready for a new request.

- C. Recognizing that SCmdAccept is not asserted, the master holds all request phase signals (MCmd, MAddr, and MData). The slave asserts SCmdAccept in the next cycle, for a request-accept latency of 1.

- D. The slave captures the write address and data.

- E. After 1 idle cycle, the master starts a new write request. The slave deasserts SCmdAccept.

F. Since SCmdAccept is asserted, the request phase ends. SCmdAccept was low for 2 cycles, so the request-accept latency for this transfer is 2. The slave captures the write address and data.

#### Request Handshake and Separate Response

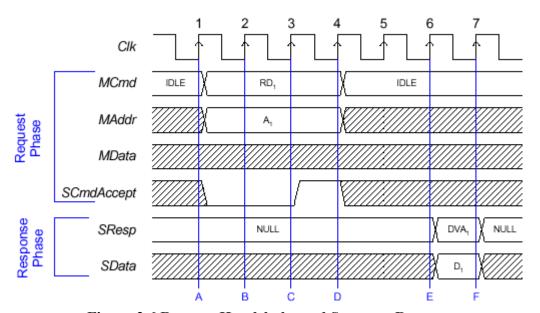

Figure illustrates a single read transfer in which a slave introduces delays in the request and response phases. The request accept latency 2, corresponds to the number of clock cycles that SCmdAccept was deasserted. The request to response latency 3, corresponds to the number of clock cycles from the end of the request phase (D) to the end of the response phase (F).

Figure 2.6 Request Handshake and Separate Response

#### Sequence

A. The master starts a request phase by issuing the RD command on the MCmd field. At the same time, it presents a valid address on MAddr. The slave is not ready to accept the command yet, so it deasserts SCmdAccept.

- B. The master sees that SCmdAccept is not asserted, so it keeps all request phase signals steady. The slave may be using this information for a long decode operation, and it expects the master to hold everything steady until it asserts SCmdAccept.

- C. The slave asserts SCmdAccept. The master continues to hold the request phase signals.

- D. Since SCmdAccept is asserted, the request phase ends. The slave captures the address, and although the request phase is complete, it is not ready to provide the response, so it continues to drive NULL on the SResp field.

- E. The slave is ready to present the response, so it issues DVA on the SResp field, and drives the read data on SData.

- F. The master sees the DVA response and captures the read data.

#### **Burst Read**

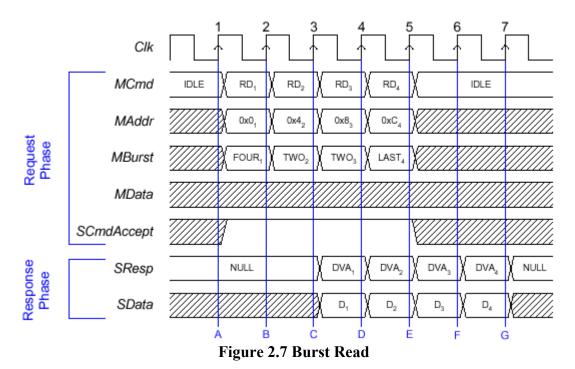

Figure 2.7 illustrates a burst read transaction that is composed of four-pipelined burst read transfers. An additional field, MBurst, is added to the request phase, indicating the type of the burst and the number of transfers that the master expects. In this diagram, MData and SData are assumed to be 32 bits.

#### Sequence

A. The master starts the burst read by driving RD on MCmd, the first address of the burst on MAddr, and the burst code FOUR on MBurst. The burst code indicates that this is an incrementing burst and that four or more transfers are expected. The slave is ready for anything, so it asserts SCmdAccept.

- B. The master issues the next read in the burst. MAddr is set to the next word-aligned address. For 32-bit words, the address is incremented by 4.The master also changes MBurst to TWO, meaning that two or more transfers remain in the transaction.

- C. The master issues the next read in the burst, incrementing MAddr and leaving MBurst set to TWO, because there are still two or more transfers remaining. The slave is now ready to respond to the first read in the burst, so it drives DVA on SResp and valid data on SData. The request-to-response latency for this transfer is 2.

- D. The master issues the final read in the burst, incrementing MAddr and setting MBurst to LAST. The master also captures the data for the first read from the slave. The slave

responds to the second transfer. The request-to-response latency for this transfer is 2, although it is possible for the slave to introduce more latency for each response in a burst transaction. (In OCP, bursts do not impose any additional constraints on protocol timing.)

- E. The master captures the data for the second read from the slave. The slave responds to the third transfer.

- F. The master captures the data for the third read from the slave. The slave responds to the fourth and last transfer.

- G. The master captures the data for the last read from the slave.

# 2.2 OCP Implementation

The OCP interface is implemented in the CPU model according to the requirements discussed in the previous sections. As described in the first chapter, the CPU model is written in C. The OCP handshake protocol is implemented in a C function bus\_interface\_process(). When a miss occurs, this function is called to initiate communication with the memory. The total clock cycles required to complete the data transfer depend on the memory latency and the OCP protocol overhead. After the start of the handshake, the function bus\_interface\_process() is executed on every clock cycle until the end of the handshake. All the variables that store different transitions of the OCP signals during the handshake are declared globally in the C program so that their values would not be lost at the end of the clock cycle. This function is capable of handling both normal and burst OCP accesses. The C source code is given in the appendix.

# 2.3 Summary

In this chapter, we have discussed various features of OCP that are used in our CPU model. This includes the description of basic OCP signals and their signaling requirements. Later, their use has been demonstrated through timing diagrams, which show different types of handshakes. As told earlier, this chapter covers very basic information about OCP. Detailed information can be found from the online manual of OCP at <a href="www.ocp-ip.com">www.ocp-ip.com</a>. The important thing to remember is that the detection of a miss causes the CPU model to initiate communication with the memory. This communication is done through OCP and is implemented in the model by a C function bus\_interface\_process().

# REFERENCES

Online manual of OCP at www.ocp-ip.com.

# **CHAPTER**

# Foreign Language Interface

As described in the first chapter, our CPU model is written in C language. However, most existing IP cores today are written either in VHDL or Verilog. In Europe, VHDL is the widely used Hardware Description Language. Therefore to make the simulation in a mixed language environment we need some interface between C and VHDL. The VHDL Foreign Language Interface (FLI) by 'Mentors Graphics' provides this interface.

The VHDL FLI allows us to replace VHDL architectures and subprogram bodies with code written in C. The FLI also provides a number of C functions to allow the VHDL database to be accessed and manipulated.

FLI has lot of features and can be used for many different tasks. This chapter only covers the portion of FLI, which is used in the thesis. Detailed information can be found from the ModelSim technical manual. However, it is our experience that the chapter concerning FLI in the ModelSim technical manual lacks some practical information that should be included for the beginner. In this chapter, we have tried to provide this information. We hope that this chapter would not only serve to understand the simulation environment of our thesis but also as a quick start guide for the beginner. It is assumed that the reader is familiar with VHDL.

# 3.1 Using VHDL FLI with Foreign Architectures

The purpose of the following discussion is not to explain FLI but to make it clear how to use FLI i.e. how we can integrate our C and VHDL code so that we can simulate in a mixed language environment.

# **TEST BENCH**

#### Figure 3.1

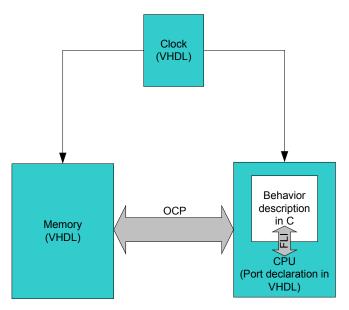

We start with the example of our test bench, which is our simulation environment. Our test bench consists of following entities:

- Clock

- CPU

- Memory

CPU is the entity whose whole behavior is described in C language. The Clock and Memory are purely in VHDL. We start with the VHDL description of the CPU. The test bench is shown in figure 3.1. The VHDL description of the CPU in which its ports and generics are declared, is shown in figure 3.2.

```

entity cpu is

generic (

input file C :string :="";

output file C:string:="";

addr width: integer;

data width: integer);

port (

nreset

: in bit;

clk

: in bit;

-- OCP signal

: in bit;

-- OCP signal

SCmdAccept

: in bit vector(1 downto 0);

-- OCP signal

SResp

: in bit vector(data width-1 downto 0);

-- OCP signal

SData

: out bit vector(2 downto 0);

-- OCP signal

MCmd

MBurst

: out bit vector(2 downto 0);

-- OCP signal

: out bit vector(addr width-1 downto 0);

-- OCP signal

MAddr

: out bit vector(data width-1 downto 0);

-- OCP signal

MData

: out bit;

cpu stall

: out bit);

cpu out

end cpu;

architecture behaviour of cpu is

attribute foreign: string;

attribute foreign of behaviour : architecture is "cpu init ./ptool.sl;";

begin

end;

```

Figure 3.2 VHDL description of CPU entity

This is all what we need to specify in VHDL.

To use the foreign language interface with C models, you first create and compile architecture with the FOREIGN attribute. The string value of the attribute is used to specify the name of a C initialization function and the name of an object file to load. When ModelSim elaborates the architecture, the initialization function is called. Parameters to the function include a list of ports and a list of generics.

Starting with VHDL93, the FOREIGN language attribute is declared in package STANDARD. With the 1987 version, you need to declare the attribute yourself. You can declare it in a separate package, or you can declare it in the architecture that you are replacing. (This will also work with VHDL93).

The value of the FOREIGN attribute is a string containing two parts. For the following declaration:

attribute foreign of behaviour : architecture is "cpu\_init ./ptool.sl";

The attribute string parses this way:

#### cpu\_init

The name of the initialization function for this architecture. This part is required.

#### ptool.sl

The path to the shared object file to load. This part is required.

In our example we have used only two parameters and these are both required. Some optional parameters can also be used whose details can be found from the ModelSim manual.

In our example the cpu\_init() function is written in the C file ptool.c. The file ptool.sl is generated by compiling and linking ptool.c using GNU compiler. So when the ModelSim loads the CPU entity it searches for the file ptool.sl where all the behavior of the CPU entity is elaborated. Normally the .so extension is used but on HP machines (which we are using) .sl extension is used.

If the initialization function has a leading '+' or '-', the VHDL architecture body will be elaborated in addition to the foreign module. If '+' is used (as in the example below), the VHDL will be elaborated first. If '-' is used, the VHDL will be elaborated after the foreign initialization function is called.

# 3.1.1 The C initialization function

This is the entry point into the foreign C model. The initialization function typically:

- Allocates memory to hold variables for the instance

- Registers a callback function to free the memory when ModelSim is restarted

- Saves the handles to the signals in the port list

- Creates drivers on the ports that will be driven

- Creates one or more processes (a C function that can be called when a signal changes)

- Sensitizes each process to a list of signals

The ModelSim FLI has provided a lot of library functions and types, which are declared in the header file **mti.h**. The type mtiSignalIdt is used for the input signals of the entity (in VHDL) and the type mtiDriverIdt is used for the output signals. In the VHDL description of the CPU entity the signals nreset, clk, SCmdAccept, SResp and SData are the input signals so they are declared as type mtiSignalIdT and the output signals of the cpu entity are MCmd, MBurst, MAddr MData, cpu\_stall and cpu\_out and they are declared as types mtiDriverIdT in the C program of the CPU model. So these are declared

as shown below in figure 3.3. Note that names of the signals should be the same as in VHDL.

```

typedef struct {

mtiSignalIdT nreset;

mtiSignalIdT clk;

mtiSignalIdT SCmdAccept;

mtiSignalIdT SResp;

mtiSignalIdT SData;

mtiDriverIdT MCmd;

mtiDriverIdT MBurst;

mtiDriverIdT MAddr;

mtiDriverIdT MData;

mtiDriverIdT cpu_stall;

mtiDriverIdT cpu_out;

} inst_rec;

```

Figure 3.3 : Declaration in C

Now we look at the <code>cpu\_init()</code> function. This function is executed when we load the CPU entity in ModelSim .In addition to specifying inputs, outputs and sensitivity we can also use that function to initialize other variables which has to be used later in the code. We can also add file read/write functions and anything, which we need to use just like a normal C program. Only the part of the <code>cpu\_init()</code> function, which is used to interface with VHDL, is shown in figure 3.4.

```

void cpu init(

mtiRegionIdT

region,

*param.

mtiInterfaceListT *generics,

mtiInterfaceListT *ports

inst rec

*cpu ip;

mtiProcessIdT cpu proc;

mtiSignalIdT outp;

cpu ip = (inst rec *)mti Malloc(sizeof(inst rec));

mti AddRestartCB(mti Free, cpu ip);

/* Here we can add our additional code. This can be found in the Appendix. */

cpu ip->clk = mti FindPort(ports, "clk");

cpu ip->nreset = mti FindPort(ports, "nreset");

cpu ip->SCmdAccept = mti FindPort(ports, "SCmdAccept");

cpu_ip->SResp = mti_FindPort(ports, "SResp");

cpu ip->SData = mti FindPort(ports, "SData");

outp = mti FindPort( ports, "cpu_out" );

cpu ip->cpu out = mti CreateDriver( outp );

cpu ip->MCmd = mti CreateDriver(mti FindPort(ports, "MCmd"));

cpu ip->MBurst = mti CreateDriver(mti FindPort(ports, "MBurst"));

cpu ip->MAddr = mti CreateDriver(mti FindPort(ports, "MAddr"));

cpu ip->MData = mti CreateDriver(mti FindPort(ports, "MData"));

cpu ip->cpu stall = mti CreateDriver(mti FindPort(ports, "cpu stall"));

cpu proc = mti CreateProcess("cpu process", cpu process, cpu ip);

mti Sensitize(cpu proc, cpu ip->clk, MTI EVENT);

mti Sensitize(cpu proc, cpu ip->nreset, MTI EVENT);

```

Figure 3.4 : C initialization function cpu init()

We have declared a pointer \*cpu\_ip of type inst\_rec. This pointer is used to point the variables of inst\_rec, which are basically the input and output signals of the CPU entity. Then we have used ModelSim FLI library functions whose detail is given below:

#### void mti AddRestartCB(mtiVoidFuncPtrT func, void \*param)

Causes the specified function to be called before the simulator is restarted. The function is passed the parameter specified by "param", and it should free any memory that was allocated.

#### void \*mti\_Malloc(unsigned long size)

Allocates a block of memory of the specified size and returns a pointer to it. The memory is initialized to zero. On restore, the memory block is guaranteed to be restored to the same location with the values contained at the time of the checkpoint. This memory can be freed by mti\_Free(). It cannot be freed by a call to the free() C-library function.

#### mtiSignalIdT mti\_FindPort(mtiInterfaceListT \*list, char \*name)

This function searches linearly through the specified interface list and returns the signal ID of the port whose name matches the one specified. It returns NULL if it does not find the port. The search is not case-sensitive. So this function is used for all the input and output ports of the CPU entity. As shown in the code of cpu\_init() function, all the input and output signals nreset, clk, SCmdAccept, SResp, SData, MCmd, Mburst, Maddr, Mdata, cpu\_stall and cpu\_out are specified using mti\_FindPort() function.

#### mtiDriverIdT mti\_CreateDriver(mtiSignalIdT sig)

Creates a driver on a signal. A driver must be created for a resolved signal in order to be able to drive values onto that signal and have the values be resolved. Multiple drivers can be created for a resolved signal, but no more than one driver can be created for an unresolved signal. This function is used for all the output signals of the entity. In our example the output signals are MCmd, MBurst, MAddr, MData, cpu\_stall and cpu\_out, which are used alongwith mti\_FindPort() function.

# mtiProcessIdT mti\_CreateProcess(char \*name, mtiVoidFuncPtrT func, void \*param)

Creates a new process. The parameter "name" is the name that will appear in the Simulator's process window, which in our case is cpu\_process. If the process is created during elaboration, the specified function will be called at time 0 after all the signals have been initialized. The mti\_Sensitize() and mti\_ScheduleWakeup() functions can be used to cause the function to be called at other times. When the function is called, it is passed the parameter specified by "param".

# void mti\_Sensitize(mtiProcessIdT proc, mtiSignalIdT sig, mtiProcessTriggerT when)

Causes the specified process to be called when the specified signal is updated. If the when parameter is MTI\_EVENT, then the process is called when the signal changes value. If the when parameter is MTI\_ACTIVE, then the process is called whenever the signal is active. Since the CPU is strictly sequential so it is only sensitive to nreset (reset signal) and clk (clock) signal. So whenever the nreset or clk signal changes this process cpu\_process() function is called. The nreset signal is only used at the beginning for initialization.

#### Input sensitive function

So cpu\_init() function is used for initialization and cpu\_process() function is used to describe the functionality of the CPU on every clock cycle. Again, only the portion of cpu\_process() related to FLI is shown here.

```

static void cpu_process( inst_rec *cpu_ip )

int clk,nreset;

int SCmdAccept;

int count, stall;

char SData[DATA_WIDTH], MData[DATA_WIDTH], MAddr[ADDR_WIDTH];

char MCmd[3];

char SResp[2];

clk

= mti_GetSignalValue( cpu_ip->clk );

= mti_GetSignalValue( cpu_ip->nreset );

SCmdAccept = mti_GetSignalValue( cpu_ip->SCmdAccept);

mti_GetArraySignalValue(cpu_ip->SResp,SResp);

mti_GetArraySignalValue(cpu_ip->SData,SData);

convert(&clk,1);

convert(&nreset,1);

convert(&SCmdAccept,1);

count=clk;

if(nreset==0)

{ count=0;

stall=0;

bus active=0;

convert(&count,0);

convert(&stall,0);

MCmd[0]=MCmd[1]=MCmd[2]= BIT_0;

mti_ScheduleDriver( cpu_ip->MCmd,(long)MCmd, 0, MTI_INERTIAL );

mti_ScheduleDriver( cpu_ip->cpu_out,count, 0, MTI_INERTIAL );

mti_ScheduleDriver( cpu_ip->cpu_stall, stall, 0, MTI_INERTIAL );

else if(clk==1)

{convert(&count,0);

convert(&stall,0);

/* the functionality of cpu is described here. Complete version is

given in Appendix*/

mti_ScheduleDriver( cpu_ip->cpu_out,count, 0, MTI_INERTIAL );

mti_ScheduleDriver( cpu_ip->cpu_stall, stall, 0, MTI_INERTIAL );

mti_ScheduleDriver( cpu_ip->MCmd,(long)MCmd, 0, MTI_INERTIAL );

mti_ScheduleDriver( cpu_ip->MAddr,(long)MAddr, 0, MTI_INERTIAL );

mti_ScheduleDriver( cpu_ip->MData,(long)MData, 0, MTI_INERTIAL );

}

}

```

Figure 3.5 cpu process()

As evident the process cpu process only runs when there is a change in clock signal. To make it sensitive only with the positive edge of the clock, all the code is written under the "if" condition: clk=1. For all the input and output signals the corresponding variables have been declared. Hence the signals nreset, clk and SCmdAccept, which are single bit signals, are declared as integers of type int. And the signals having more than one bit SData, MData, MAddr, MCmd and SResp as arrays of type char having length equal to their bit width. The input variables get the values from the VHDL environment from the FLI functions mti GetSignalValue() and mti GetArraySignalValue(). These variables have been updated every time when the process runs and are then assigned to their corresponding signals by the function mti ScheduleDriver(). All the input signals to CPU entity are generated by the entities, which are in VHDL. By using the FLI library functions (which are used in cpu init() function and cpu process() function) these values of these signals are assigned to their corresponding variables in cpu process() function. Based on these values we update the output variables whose values are in turn assigned to the output signals of CPU entity. These output signals are inputs to memory, which is again an entity fully in VHDL.

# 3.1.2 Some important issues

- 1. The logic level '1' in VHDL is equivalent to 3 in C and logic level '0' is equivalent to We use our own simple function convert() which convert the input signal values from integer 3 to integer 1, integer 2 to integer 0 and vice versa for the output signals. This is done just to make the code more readable.

- 2. As described earlier that the signals having more than one bit have been used as characters. These signals are of type bit\_vector in VHDL. To deal with these signals in C, we have declared a type of enumerated data.

```

typedef enum {BIT 0, BIT 1} bit;

```

If we want to assign logic level '0' to a particular bit we assign it BIT\_0 and for logic level '1' we assign BIT\_1. Thus if we want to assign "001" to the three bit signal MCmd, it would be as follows:

```

MCmd[0]=BIT_0;

MCmd[1]=BIT_1;

MCmd[2]=BIT_1;

```

- 3. Since cpu\_process() is basically a C function so all the variables declared inside are actually local variables i.e. they lost their values at the end of the function. Therefore if we want for some variables to retain their values after the function, they must be declared globally.

- 4. To get the values of generics specified in VHDL, the pointer \*generics is used as shown in C initialization function cpu\_init(). The pointer \*generics is of type mtiInterfaceListT which is declared in the header file mti.h. Consider the example of our model in which the two generics specified in VHDL are input file C and output file C

and they are of type string. As evident from the name, the user provides the names of the input and output files through these generics. The name of the files can be retrieved in the C program by using the \*generics pointer as shown below:

```

if( (fptr1= fopen(generics->u.generic_array_value,"r")) ==NULL)

{

printf("\n Couldn't open the file %s",generics->u.generic_array_value);

}

if( (fptr2= fopen(generics->nxt->u.generic_array_value,"w")) ==NULL)

{

printf("\n Couldn't open the file %s",generics->nxt->u.generic_array_value);

}

```

A linked list is created in header file mti.h and successive generic elements can be retrieved by using the pointers shown in the above example.

## 3.2 SUMMARY

The FLI is used to make communication between entities written in C and in VHDL. The entity whose behavior is described in C is still has its port declaration in VHDL. But in its architecture description in VHDL, the name of the 'C initialization function' and 'C shared file' containing this function is specified. In the 'C shared file' the complete behavior of the entity is elaborated. When the entity is loaded in the simulator the control is transferred to that 'C initialization function'. This function uses FLI library functions to transfer the information about the ports and generics of the entity, which are specified in its VHDL declaration. It also specifies different functions, which are sensitive to the input signals of this entity. Whenever these inputs change, the corresponding functions are executed. Whenever these functions are executed they update some variables, which are basically the updated values of the output signals of the entity. The FLI library functions then convert these values according to VHDL standards so that can be understood by the entities written purely in VHDL and vice versa.

In this chapter we have described, how we can simulate in a mixed language environment by using FLI. The FLI has lot of features and options available and there is lot of ways to do same things. We have used which is most simple and we have covered only those features, which are required in our task.

# REFERENCES

Foreign Language Interface (FLI), Mentors Graphics' ModelSim Technical Manual.

### CHAPTER

# An Overview of the CPU Model

Now we know about OCP and FLI and also how they are used in the model. In this chapter, we will describe the overall structure and working of our CPU model. We start with some features of general-purpose microprocessors and then we will explain how these features are included in our model.

# 4.1 An overview of the General-purpose Microprocessor

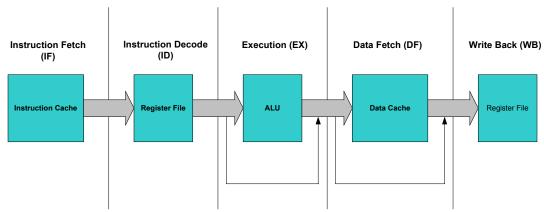

To make a model of the processor we need to study the features and functionality of the processors used today. All processors today are pipelined and have separate instruction and data cache. In a given clock cycle more than one instruction are in progress. Their number depends on the depth of the pipeline. The modern processors used today are very complex. To increase the throughput the parallelism among instructions is exploited by out of order execution [1] and more than one instruction may be issued in every clock cycle [2]. However, in our model we haven't targeted these architectures. Our model is focused on the processors used in embedded applications. These processors are not as much complex like the processors used in Personal Computers, Workstations or High end Servers. Their architecture is much simpler than that and the pipeline scheme is also not that much complex. The instruction execution is also in order and in a given pipeline stage only one instruction is active. In most embedded processors the pipeline depth is between 5 to 8 stages [3]. ARM processor is one of them, which is largely used, in embedded applications. Therefore we can focus ourselves to study the behavior of these processors and try to include this behavior in our model.

Let's have a quick look on a five stage pipelined processor [4] with separate instruction and data cache. The first stage of the pipeline is called Instruction Fetch stage in which the processor fetches instruction from the instruction cache by generating the instruction address. In some processors this Instruction Fetch stage is further divided into two stages to decrease the clock period. The next step is to decode the instruction, which is normally

called Instruction Decode (ID) stage. The instruction is decoded and the specified registers are accessed. In most architectures if the instruction is Jump or Branch some action has been taken in the ID stage that involve change in the next instruction target address. The next stage is called the Execution stage where the instruction is treated according to its type. If it is an R-Format instruction (instruction that require arithmetic operation by ALU on its operands) then some arithmetic or logical operation is performed in the ALU (Arithmetic Logic Unit) and in the case of a load or store instruction the memory address has been calculated. The next stage is the memory stage where the data cache is accessed for either data read or data write. And the last stage is Write Back stage where the output of the ALU or the data from the memory is written into the register file.

Figure 4.1 Five-stage Pipeline MIPS R1000

In the ideal case, every instruction consumes one clock cycle and the CPI (cycles per instruction) is 1. In Superscalar machines where more than one instruction can be issued in a clock cycle the ideal CPI can also be decreased from 1. However, these machines are not the targets in our model. The actual CPI is always greater than 1 due to structural, data and control hazards. There are also instructions like multiply/divide that consume several clock cycles, and depending upon the frequency of these instructions the CPI increases. But the most dominant factor is the misses produced during the execution.

There are only two cases when the processor needs to communicate with the memory:

- When the instruction miss occurs

- When the data miss occurs

The instruction cache is accessed in every clock cycle. So there is always a probability that an instruction miss can occur. Thus in the first stage if the instruction is not found in the instruction cache, instruction miss occurs and the CPU has to fetch the instruction from the memory. This involves consumption of many cycles depending on the latency of the memory. When the instruction is brought in the cache the normal execution continues.

Data miss can only occur in the case of load or store instruction and also when these instructions result in a data miss. All other types of instructions that do not access data cache cannot generate data misses. Because of these reasons, instruction misses are higher than data misses in most programs. However, the opposite is also true in many programs. In the case of load or store instruction, when the miss arises in the data cache, the pipeline is stalled and remains stalled until the required data reaches the data cache from the memory. There are two types of data misses: read misses and write misses. In the case of a read miss the CPU initiates communication with the memory to read some data elements while in the case of a write miss the CPU initiates communication to write on some particular location in the memory.

The instruction miss and the data read miss are similar in terms of communication with the memory. Whenever any of these misses occur, the access to the memory is 'burst access'. An access to the memory brings the next four instructions or data items from the memory into the cache to exploit spatial locality. However, write accesses to the memory are not burst accesses. When memory is accessed for write operation, only one location in the memory is updated. The 'burst access' occupies the bus for a greater number of clock cycles as compared to normal access as shown in section 2.1.3 where both the normal and burst OCP accesses are shown.

There are two kinds of write policies in cache designs: write through and write back. In write through scheme, the information is written to both the block in the cache and to the block in the memory. So in this scheme every store instruction results in a write miss. In write back scheme, the information is written only to the block in the cache. The modified block is written to the memory only when it is replaced.

So whenever a miss occurs, the pipeline is stalled and remains stalled until the corresponding miss is handled. It may happen that the instruction and data miss occurs at the same time then both the misses are handled one by one with the data miss to be handled first so that the pipeline can continue. These factors increase the completion time of an individual instruction, which in ideal case is 1 clock cycle. We can say that if there is no miss or no other hazard then at the end of every clock cycle one instruction is completed other wise it is not.

Some processors also have second-level cache that is bigger than the first-level caches. It can be a unified cache that is used for both data and instruction or it may be a case that there are separate instruction and data second-level caches. When there is a miss in the first-level cache then before accessing the memory, second-level cache is accessed. If the required instruction or data is found in the second-level cache it is supplied to the first-level cache otherwise the memory is accessed. In the case of a hit in the second-level cache the penalty for accessing the second-level cache is lesser than accessing the memory. But in the worst case when there is a miss in the second-level cache the miss penalty is the number of clock cycles to access the second-level cache plus the number of clock cycles to access the second-level cache plus the number of clock cycles to access the memory. The effective miss rate in the presence of second-level cache is the product of the individual miss rates of both first-level and second-level caches.

As described in the first chapter, our aim is to generate traffic on the bus in a realistic manner. Therefore, in the above discussion we have focused ourselves on the factors, which generate traffic on the bus connecting the CPU and memory. Following are the important observations from the above discussion:

- In ideal case, every instruction requires 1 clock cycle in a pipelined processor.

- In every clock cycle, the number of active instructions is usually equal to the depth of the pipeline.

- In every clock cycle, there is a probability that an instruction miss or data miss or both can occur.

- When a miss occurs, memory is accessed and the pipeline is stalled. The pipeline remains stalled until the required data is brought into the cache.

- Instruction misses and data read misses generate burst access to the memory while the write misses generate single access.

Based on this information we made our model which include the behavior of all these phenomenon discussed above

# 4.2 Structure and working of the model

We will start the discussion of our model with the explanation of the basic input parameters of the CPU model and then we will show how the necessary data is collected from these inputs. Later, we will show how the model is organized into different parts and then we will describe the overall sequence of operation during the whole simulation.

# 4.2.1 Basic inputs of the model

The basic input parameters are supplied by the user to carry out the simulation. These inputs are written in a specially designed file, which is made for this model. These basic inputs are the required inputs and are necessary to carry out the simulation. In addition to these basic inputs there are also some optional inputs, which will be discussed in the next chapter. The basic inputs are given below:

- Total number of instructions

- Percentage of load instructions

- Percentage of store instructions

- Instruction miss rate

- Data miss rate

- CPI (including the effect of structural, data and control hazards)

- Memory Access startup latency (Number of cycles required to initiate memory transfer after detecting a miss)

- Memory Accesses end latency (Number of cycles required to restore the normal execution after the completion of memory transfer)

- Seed for the random functions

The 'total number of instructions' tells us about the total number of instructions which we have to simulate. These 'total number of instructions' are not the total number of instructions, which we can found in the assembly program. They are the total number of instructions, which are actually executed. For e.g., if there is a loop consisting of 10 instructions and that loop runs for 100 times then the total number of instructions that are executed are 1000 not 10.

'Percentage of load instructions' and 'Percentage of store instructions' tell us how many instructions are load/store from the total number of instructions. These are the instructions that may cause a data miss. These two parameters and 'Data miss rate' also help us to distinguish between read and write misses as these two misses have different behaviors on the bus.

'Instruction miss rate' and 'Data miss rate' tell us about how many data and instruction misses are generated during the execution of the total number of instructions. We have to generate these misses in a manner that resembles to a real traffic.

The basic input CPI (cycles per instruction) tells the CPI without taking into account the effect of the misses. However, the CPU model demands that this input CPI includes the effect of different data, control and structural hazards. The reason for this demand is that the CPU model can't include the effect of these hazards by itself because of the absence of real software. However, even if the user provides the ideal CPI it doesn't have a very remarkable affect on the simulation. Therefore, the ideal CPI can also serves the purpose.

'Memory Access startup latency' is the number of clock cycles required to initiate memory transfer after detecting a miss. Nearly all processors, after detecting a miss can't initiate communication with the memory in the same cycle. Generally it is started at the start of the next cycle and in some processors depending upon their pipeline technique more than one clock cycle is required. Similarly, 'Memory Accesses end latency' is the number of clock cycles required to restore the normal execution after the completion of the memory transfer and is different for different processors.

The input 'Seed for random functions' is any integer number, which is used as a seed in different random functions in the C program of the model.

# 4.2.2 Execution clock cycles

By using the values of these inputs the CPU model generates traffic on the bus. Based on these parameters we can approximate the total number of clock cycles required to complete the given number of instructions. The total number of clock cycles in which the CPU does some useful work is given by (let's call it Execution clock cycles):

Execution clock cycles =

$$CPI \times Total$$

number of instructions (4.1)

The parameter 'Execution clock cycles' is one of the most important parameters of our model. The 'Execution clock cycles' to complete the given number of instructions remain

constant and is independent of memory latency and bus arbitration. In this chapter and in the next chapter, whenever we use the term 'Execution clock cycles', we mean the effective clock cycles in which the CPU is perfectly in execution i.e. the number of clock cycles during which the CPU is not stalled.

If we take into account the misses occurred during the execution, the total number of clock cycles will be:

Total number of clock cycles = Execution clock cycles + Total number of misses  $\times$  Miss penalty (4.2)

Where,

Total number of misses = instruction misses + data misses

Total Execution time = Total number of clock cycles  $\times$  Clock period (4.3)

Thus before the start of the simulation, we can calculate the Execution clock cycles from the CPI and the total number of instructions, which are the user-supplied inputs. We also know the total number of misses, which have to be introduced within these Execution clock cycles. However, we can't calculate the Total number of clock cycles by using equation 4.2 because we don't know about the Miss penalty i.e. the number of clock cycles required to access the memory. Different memories have different miss penalties and the miss penalty for the same memory may be different in the same simulation depending upon the traffic on the bus. It may happen that when CPU initiates communication with the memory, the memory is busy handling request from some other component of the SOC design and causes the CPU to stall for the clock cycles more than the latency of the memory. Hence we can only know about the total number of consumed clock cycles (to execute the given number of instructions) only at the end of the simulation. However, we can calculate the Total execution cycles and we can use it in our model.

As already described, no real software is running on our model, so during the simulation we have to make some guess whether in a given cycle we have any kind of miss or not. If we don't have a miss we can say that one instruction is completed other wise instruction is not completed. This process is repeated until the given number of instructions has been completed i.e. the Total execution cycles are completed. Chapter 5 is dedicated to the discussion about how we make the decision about a miss in a given cycle.

Before the start of the actual simulation, the CPU model is initialized with the total number of execution cycles and the total number of misses and with lots of other data elements that will be used during the simulation. A variable is initialized that counts the execution clock cycles. This counter increment by one in every useful clock cycle. When this count becomes equal to the Total execution clock cycles, the simulation is ended. In every clock cycle separate functions are called to make decision about the misses. If there is no miss then the normal execution continues. In the other case, when a miss has been found the model initiates communication with memory. During this whole memory

access, the CPU remains stalled i.e. not doing useful work. So the execution clock cycle counter does not increment during this period. When the memory transfer is completed the normal execution continues i.e. execution clock cycle counter starts incrementing again after every useful clock cycle.

# 4.2.3 Three major parts of the model

The whole model is divided into three major parts. Each part consists of a group of functions to carry out a particular task.

- A set of initialization functions that takes control from VHDL through FLI. This part is explained in chapter 3.

- A set of functions that communicates with the outside world like memory through OCP. This involves updating of the signals that communicates with the memory and the variables that keep track of the transitions occurred during the handshaking. The signals transitions are according to OCP as explained in chapter 2

- A set of functions that takes care of the generation of misses during the simulation. They are divided into parts. The first part consists of initialization functions that initializes the model with the input parameters and makes necessary calculation that will help in the rest of the simulation. The second part consists of functions that make decision about a miss in a given cycle

The third part contributes the major part of the model and is explained in Chapter 5.

# 4.2.4 Sequence of Operations

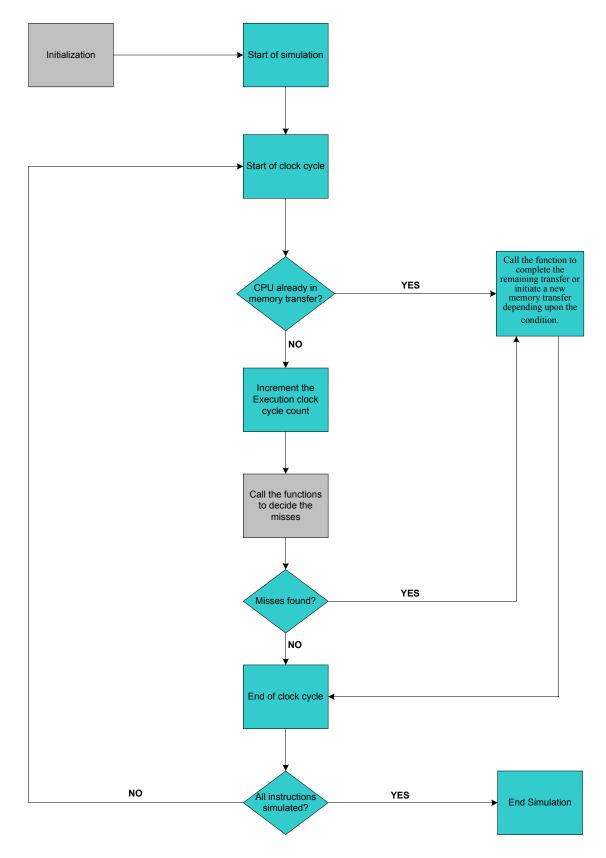

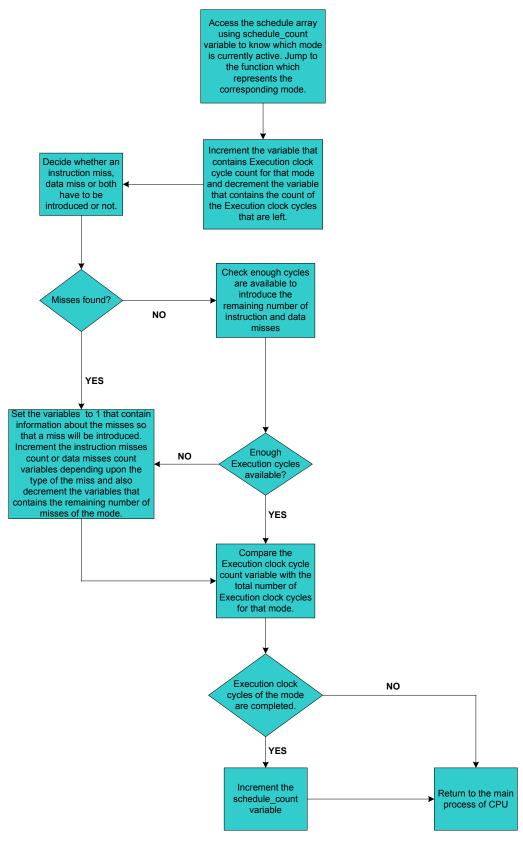

The whole simulation is carried out in the following sequence. All these steps are shown in figure 4.2.

1. Initialize the CPU model with the variables that contain the values of the input parameters i.e. total number of instructions, load/store instructions, instruction miss rate, data miss rate etc and make some necessary calculations. The inputs are read from the file by using C file read functions. The initialization takes place when we load the design in the simulator (Modelsim) window. This step is called 'Initialization' and is shown as the grey shaded region in figure 4.2. This part is explained in detail in Chapter 5.

All the remaining steps are performed during the simulation i.e. in each clock cycle the model undergoes the following steps.

2. Check at the start of each cycle if the CPU is in some stage of memory transfer. This can be seen by checking the variable, which shows whether CPU is stalled or

not. If the CPU is stalled then it is already in the communication phase i.e. communicating with the memory through OCP, which requires some cycles to complete. In that case call the function bus\_interface\_process(), which is responsible for the memory transfer. The function also checks the current status of the handshaking and takes necessary actions accordingly. This step is repeated in every clock cycle until the memory transfer is completed. If the memory transfer is completed then clear the variables that contain information about the misses that needs to be handled i.e. sets them to 0. If the CPU is not currently involved in memory transfer or the memory transfer is completed then go to the next step.

- 3. Increment the Execution clock cycle count.

- 4. Call the functions that make decision about the introduction of instruction and data misses in a given cycle. Update these variables according to the decision i.e. set them to 1 if a miss has been found or 0 if there is no miss. This step is also indicated as a grey shaded region in figure 4.2 and is explained in detail in the next chapter.

- 5. Check the variables that contain information about the instruction and data misses. If there is no miss then go to the next step otherwise go to step 8.

- 6. The clock cycle has ended. Save the values of all the variables that will be used in the next cycle. All necessary variables are declared globally so that their values will not be lost at the end of the function. Go to the next step.

- 7. Compare the value of the execution clock cycle count variable with the Total execution clock cycles value. If it is less than the total value then it means that the simulation is not ended yet and thus go back to step 2. If it is equal or greater than the total value then it means that all the instructions have been simulated so go to the step 9.

- 8. If a miss has been found then stall the processor model. Call the function that starts communication with the memory through OCP. Keep the processor stalled until the miss has been handled. This has been checked at the start of every cycle as shown in step2. If there is a miss in both the instruction and data then handle the data miss first and then handle the instruction miss. Go to step 6.

- 9. All the instructions have been simulated. Generate report about the total execution time of the instructions, the number of cycles in which the CPU remain stalled waiting for the memory response, the number of cycles the CPU is executing instructions, the number of clock cycles consumed in the longest handshake as well as in the shortest handshake etc. Terminate the simulation.

Flowchart of the complete process

Figure 4.2

# 4.3 SUMMARY

In this chapter, we have discussed those features of general-purpose processors, which are used in our CPU model. We have described what happens to the pipeline when a miss occurs. We have described the basic input parameters of the model and their purpose in the model. We have shown how the model is divided into three different parts and then at the end we have described the flowchart of the whole process.

From the basic parameters, the CPU calculates the total Execution clock cycles and the total number of instruction and data (read and write) misses. These misses have to be introduced by the model within these Execution clock cycles. During the simulation, the CPU model decides in every clock cycle whether a miss has to be introduced or not. The variable that counts the Execution clock cycles increments by one after every Execution clock cycle except when the CPU is stalled. When this count reaches the limit i.e. the total number of Execution clock cycles, it implies that all the instructions are completed. The model ensures that at this point all the misses have already been introduced. The simulation is then completed and the model generates the report, which tells the effective CPI that includes the effect of the misses. It also calculates the total number of clock cycles that are required to complete the execution of the given number of instructions, the number of clock cycles during which the CPU remains stalled and the longest and shortest time to complete the data transfer with the memory.

# REFERENCES

- [1] DLX using Tomasulo's algorithm, Computer Architecture A Quantitative Approach by John L Hennessy & David A Patterson

- [2] Superscalar version of DLX, Computer Architecture A Quantitative Approach by John L Hennessy & David A Patterson

- [3] ARM9 Embedded Trace Macrocell (ETM9) Technical Reference Manual

- [4] MIPS R1000, Computer Organization and Design by John L Hennessy & David A Patterson

# CHAPTER

# 5

# Miss Generation Techniques

In the previous chapter we have explained the overall structure and working of the model. The model is divided into three parts. The first part consists of set of functions that are used to transform different signals and variables' values from C to VHDL and vice versa. The second part is responsible to communicate with the memory. The third part, which is the most important part, makes necessary calculations about the misses and introduces them during the simulation. The third part is the two grey shaded regions in fig 4.2. The first two parts have already been explained in chapters 2,3 and 4. In this chapter we will explain the third part i.e. the two grey shaded regions in fig 4.2. So this chapter includes the discussion about different techniques that are used to generate the misses in the simulation.

When a miss occurs, it generates traffic on the bus. Our main aim is to generate traffic that resembles to a real traffic that occurs as a result of execution of real software on real IP cores. And to accomplish this, we have to generate misses in a manner that resembles to the misses generated in a real program.

We start with a very brief overview of caches. As evident from the above discussion, it is assumed that you have read chapter 4.

# 5.1 An Overview of Caches

Following is a quick review of some cache related concepts. The intention here is not to describe caches but to show later how these particular cache-related concepts are used in our model and also why some of these concepts are not used in our model. So we assume that the reader has enough knowledge of caches and the related concepts. The interested reader can read more about caches from [1] and [2]. Most information in this section is also taken from [1] and [2].

# 5.1.1 Cache Basics

Cache is the first level of memory hierarchy. The next instruction (to be executed) or the data item is first searched into the cache. When the CPU finds a requested data item in the cache, it is called a *cache hit*. When the CPU does not find a data item it needs in the cache, a *cache miss* occurs. A fixed-size collection of data containing the requested word, called a *block*, is retrieved from the main memory and placed into the cache. *Temporal locality* tells us that the same word is likely to be needed again in the near future, so it is useful to place it in the cache where it can be accessed quickly. Because of *spatial locality*, there is high probability that the other data in the block will be needed soon.

The time required for the cache miss depends on both the latency and bandwidth of the memory. Latency determines the time to retrieve the first word of the block, and bandwidth determines the time to retrieve the rest of this block. Bandwidth can also be taken as the width of the bus connecting the cache or CPU to the memory. A cache miss is handled by hardware and causes processors following in-order execution to pause, or stall, until the data are available.

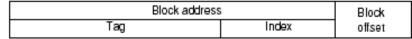

# 5.1.2 Division of address

Caches have an address tag on each block frame that gives the block address. The tag of every cache block that might contain the desired information is checked to see if it matches the block address from the CPU. As a rule, all possible tags are searched in parallel because speed is critical.

There must be a way to know that a cache block does not have valid information. The most common procedure is to add a *valid bit* to the tag to say whether or not this entry contains a valid address. If the bit is not set, there cannot be a match on this address.

Figure 5.1: Three portions of address in a set-associative or direct-mapped cache